# Simulink<sup>®</sup> PLC Coder™ User's Guide

# MATLAB&SIMULINK®

R

**R**2023**a**

#### **How to Contact MathWorks**

Latest news:

Phone:

www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

$\mathbf{\mathbf{X}}$

508-647-7000

#### The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Simulink<sup>®</sup> PLC Coder<sup>™</sup> User's Guide

© COPYRIGHT 2010-2023 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

$MathWorks\ products\ are\ protected\ by\ one\ or\ more\ U.S.\ patents.\ Please\ see\ www.mathworks.com/patents\ for\ more\ information.$

#### **Revision History**

March 2010 September 2010 April 2011 September 2011 March 2012 September 2012 March 2013 September 2013 March 2014 October 2014 March 2015 September 2015 March 2016 September 2016 March 2017 September 2017 March 2018 September 2018 March 2019 September 2019 March 2020 September 2020 March 2021 September 2021 March 2022 September 2022 March 2023

Online only New for Version 1.0 (Release 2010a) Revised for Version 1.1 (Release 2010b) Revised for Version 1.2 (Release 2011a) Revised for Version 1.2.1 (Release 2011b) Revised for Version 1.3 (Release 2012a) Revised for Version 1.4 (Release 2012b) Revised for Version 1.5 (Release 2013a) Revised for Version 1.6 (Release 2013b) Revised for Version 1.7 (Release 2014a) Revised for Version 1.8 (Release 2014b) Revised for Version 1.9 (Release 2015a) Revised for Version 2.0 (Release 2015b) Revised for Version 2.1 (Release 2016a) Revised for Version 2.2 (Release 2016b) Revised for Version 2.3 (Release 2017a) Revised for Version 2.4 (Release 2017b) Revised for Version 2.5 (Release 2018a) Revised for Version 2.6 (Release 2018b) Revised for Version 3.0 (Release 2019a) Revised for Version 3.1 (Release 2019b) Revised for Version 3.2 (Release 2020a) Revised for Version 3.3 (Release R2020b) Revised for Version 3.4 (Release R2021a) Revised for Version 3.5 (Release R2021b) Revised for Version 3.6 (Release R2022a) Revised for Version 3.7 (Release R2022b) Revised for Version 3.8 (Release R2023a)

### **Getting Started**

| Simulink PLC Coder Product Description                                                                                                                            | 1-2                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Prepare Model for Structured Text Generation                                                                                                                      | 1-3<br>1-3<br>1-3                    |

| Configure Simulink Models for Structured Text Code Generation<br>Verify System Compatibility for Structured Text Code Generation                                  | 1-3<br>1-6                           |

| Generate and Examine Structured Text Code                                                                                                                         | 1-7<br>1-7<br>1-7<br>1-8             |

| Propagate Block Descriptions to Code Comments                                                                                                                     | 1-10                                 |

| Files Generated by Simulink PLC Coder                                                                                                                             | 1-11                                 |

| Specify Custom Names for Generated Files                                                                                                                          | 1-13                                 |

| PLC IDEs for Importing Code Automatically<br>Generate and Automatically Import Structured Text Code                                                               | 1-14<br>1-14<br>1-14<br>1-14         |

| Author, Manage, and Execute Simulation-Based Tests of Generated Code                                                                                              |                                      |

|                                                                                                                                                                   | 1-16<br>1-17                         |

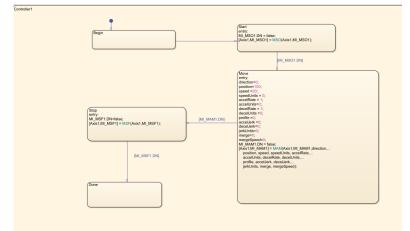

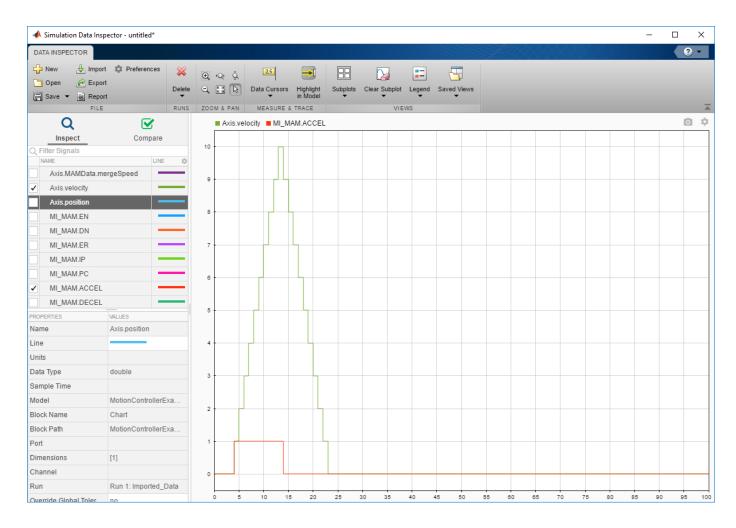

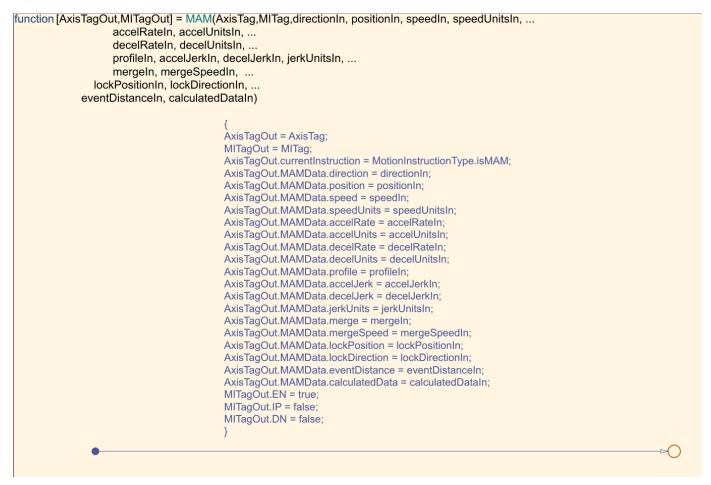

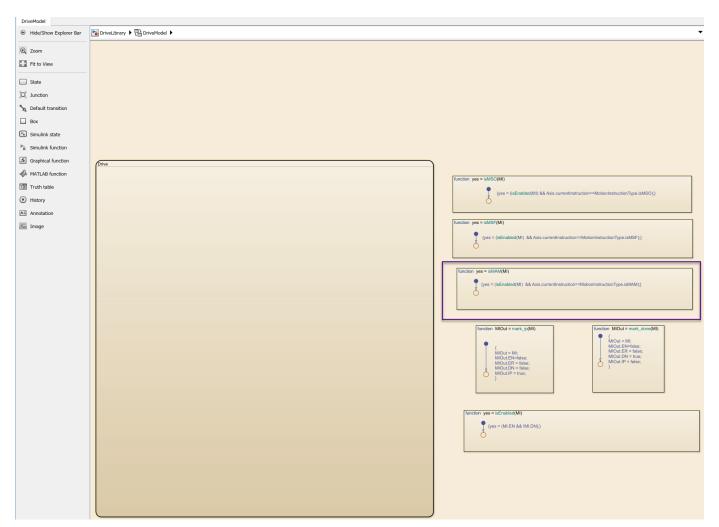

| Workflow for Using Motion Instructions in Model       Simulation of Motion API Model         Simulation of Motion API Model       Structured Text Code Generation | 1-18<br>1-18<br>1-20<br>1-21<br>1-21 |

### **Mapping Simulink Semantics to Structured Text**

# 2

| Generated Code Structure for Simple Simulink Subsystems |     |

|---------------------------------------------------------|-----|

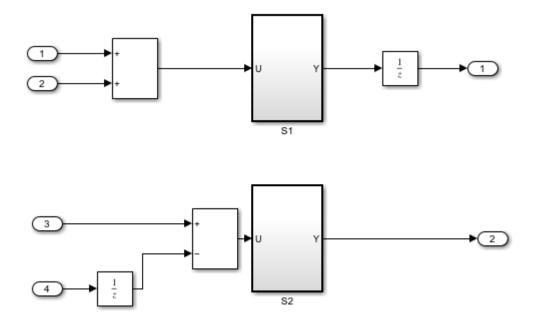

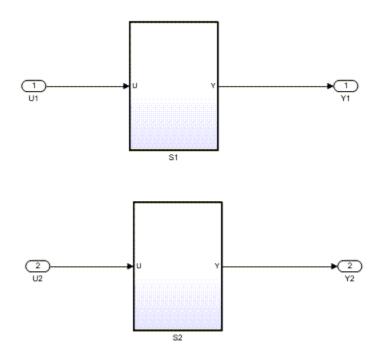

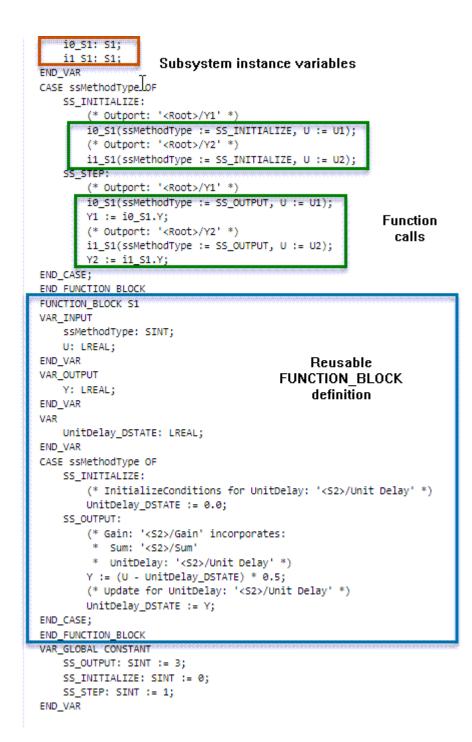

| Generated Code Structure for Reusable Subsystems        | 2-4 |

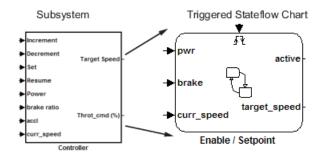

| Generated Code Structure for Triggered Subsystems                                                                                                  | 2-6               |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

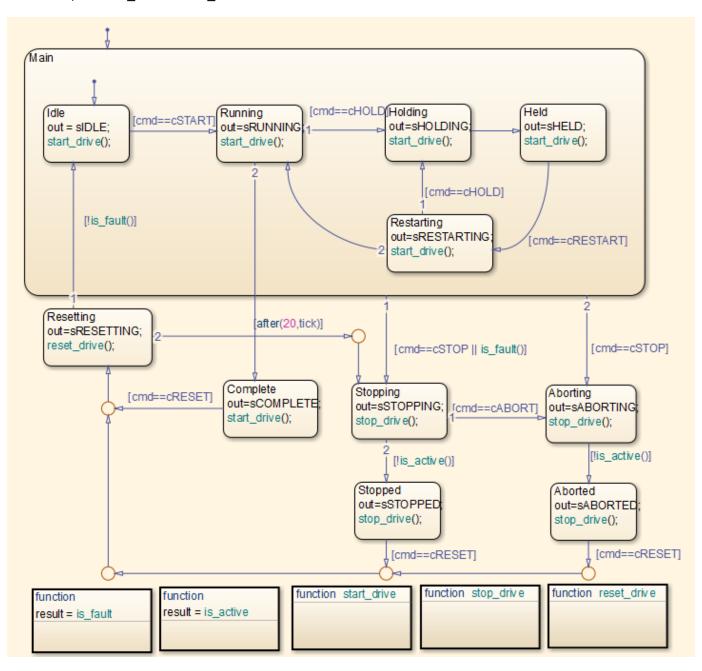

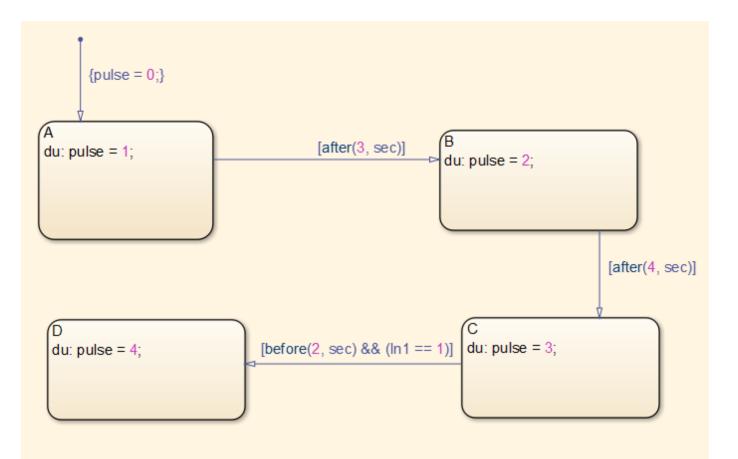

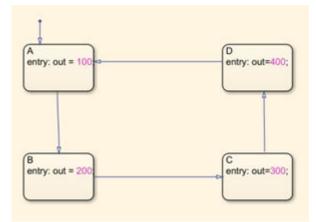

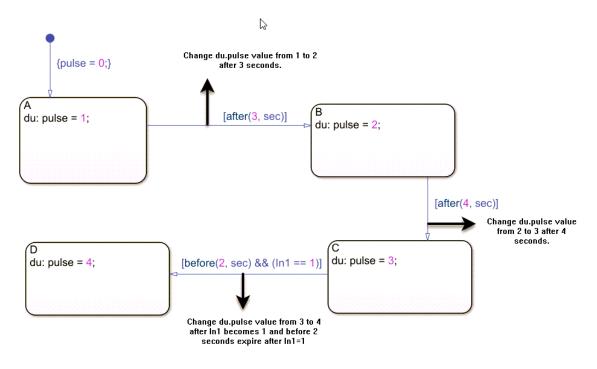

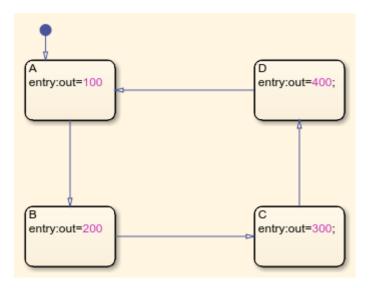

| Generated Code Structure for Stateflow Charts<br>Stateflow Chart with Event Based Transitions<br>Stateflow Chart with Absolute Time Temporal Logic | 2-8<br>2-8<br>2-9 |

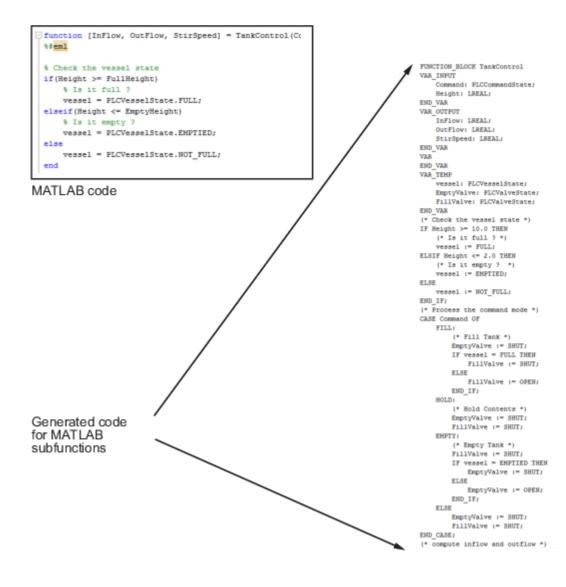

| Generated Code Structure for MATLAB Function Block                                                                                                 | 2-12              |

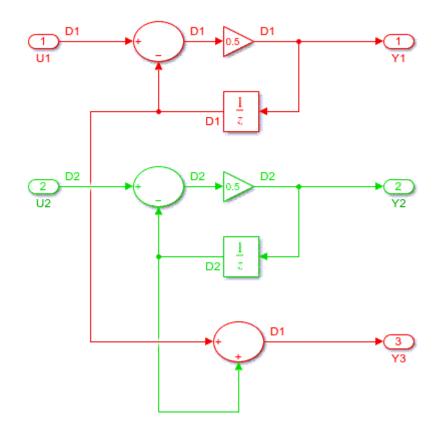

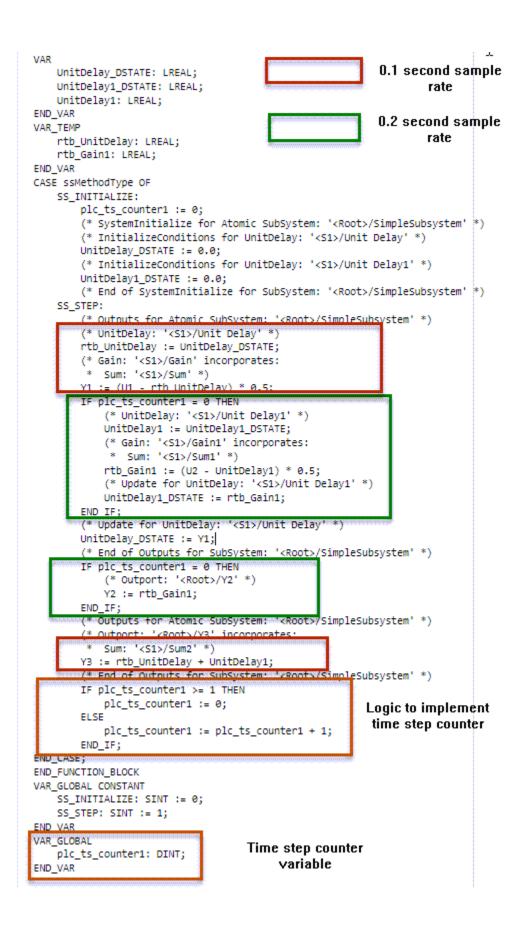

| Generated Code Structure for Multirate Models                                                                                                      | 2-14              |

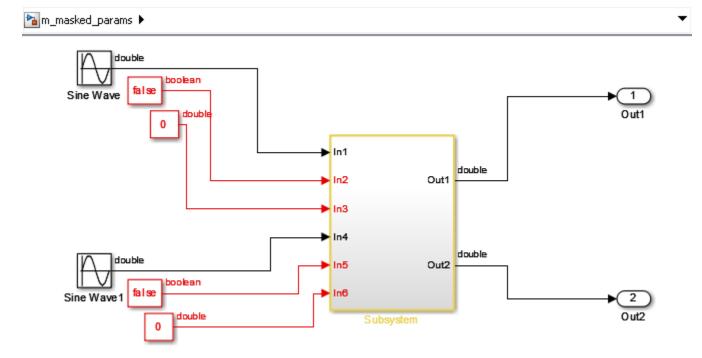

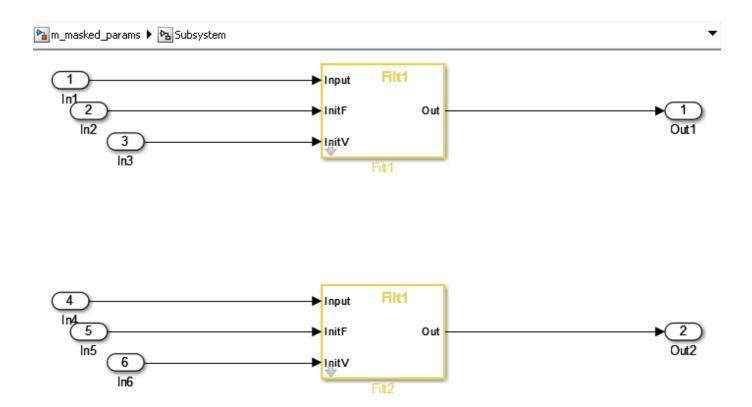

| Generated Code Structure for Subsystem Mask Parameters                                                                                             | 2-16              |

| Global Tunable Parameter Initialization for PC WORX                                                                                                | 2-20              |

| Considerations for Nonintrinsic Math Functions                                                                                                     | 2-21              |

#### **Generating Ladder Diagram**

| Supported Elements in Ladder Diagram                            |      |  |  |  |

|-----------------------------------------------------------------|------|--|--|--|

| Supported Ladder Elements                                       | 3-2  |  |  |  |

| Import L5X Ladder Diagram Files into Simulink                   | 3-4  |  |  |  |

| Model and Simulate Ladder Diagrams in Simulink                  |      |  |  |  |

| Ladder Model Simulation                                         | 3-10 |  |  |  |

| Generating Ladder Diagram Code from Simulink                    |      |  |  |  |

| Generating C Code from Simulink Ladder                          |      |  |  |  |

| Verify Generated Ladder Diagram Code                            |      |  |  |  |

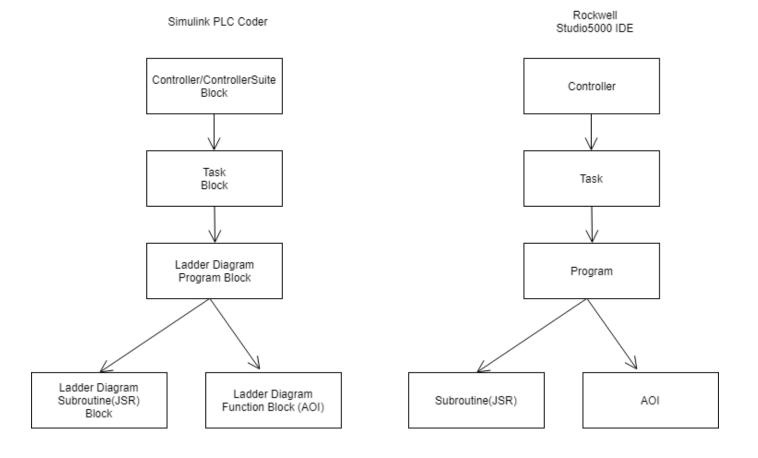

| Simulink PLC Coder Workflow vs. Rockwell Automation RSLogix IDE |      |  |  |  |

| Workflow                                                        | 3-21 |  |  |  |

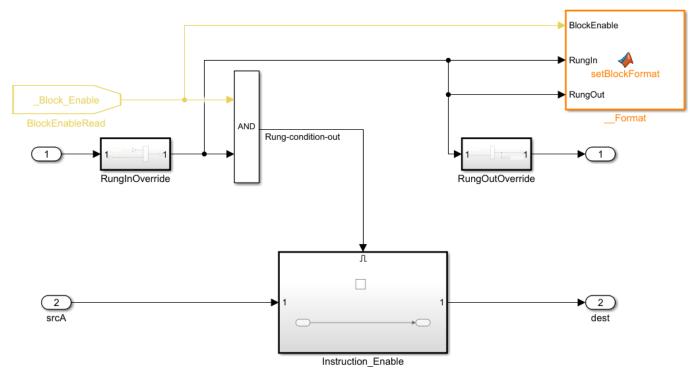

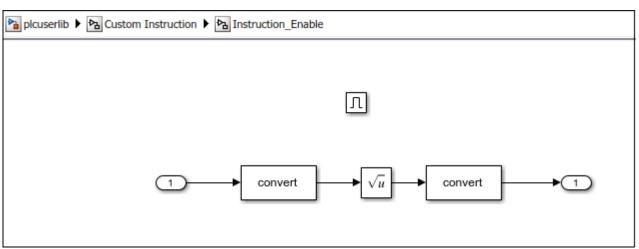

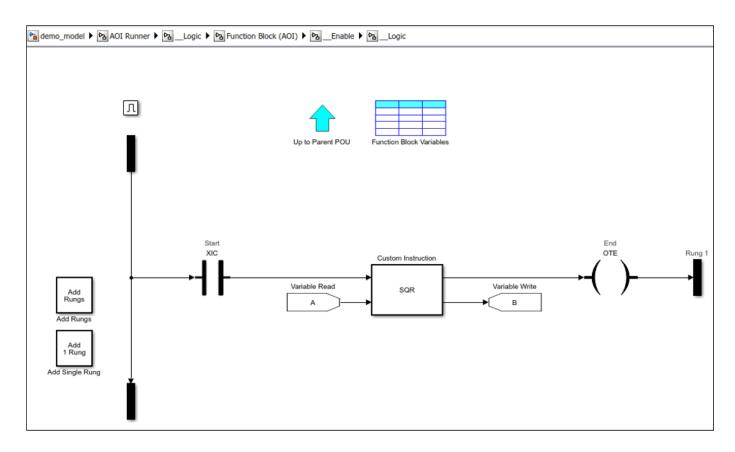

| Create Custom Instruction in PLC Ladder Diagram Models          |      |  |  |  |

| Create User-Defined Custom Instruction                          | 3-23 |  |  |  |

| Calculate Square Root by Using Custom Instruction Block         | 3-25 |  |  |  |

## **Generating Test Bench Code**

| Test Bench Verification                   | 4-2 |

|-------------------------------------------|-----|

| Integrate Generated Code with Custom Code | 4-3 |

3

| Import and Verify Structured Text Code                | 4-4        |

|-------------------------------------------------------|------------|

| Generate, Import, and Verify Structured Text          | 4-4        |

| Troubleshooting: Long Test Bench Code Generation Time | 4-4        |

| Generate Code That Has Multiple Test Benches          | 4-6        |

| Troubleshooting: Test Data Exceeds Target Data Size   | 4-8        |

| Limitations                                           | <b>4-8</b> |

5

6

### **Code Generation Reports**

| Information in Code Generation Reports                   | 5-2        |  |  |  |

|----------------------------------------------------------|------------|--|--|--|

| Create Code Generation Report                            | 5-4<br>5-4 |  |  |  |

| Limitation                                               | 5-6        |  |  |  |

| Model Web View in Code Generation Report                 |            |  |  |  |

| Model Web Views                                          | 5-7        |  |  |  |

| Browser Requirements for Web Views                       | 5-7        |  |  |  |

| Generate HTML Code Generation Report with Model Web View | 5-7        |  |  |  |

| Model Web View Limitations                               | 5-9        |  |  |  |

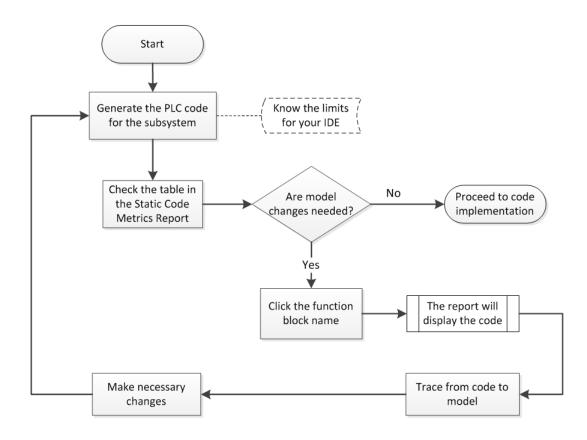

| Generate Static Code Metrics Report                      | 5-11       |  |  |  |

| Working with the Static Code Metrics Report              |            |  |  |  |

| Workflow for Static Code Metrics Report                  | 5-14       |  |  |  |

| Report Contents                                          | 5-14       |  |  |  |

| Function Block Information                               | 5-15       |  |  |  |

| View Requirements Links from Generated Code              | 5-16       |  |  |  |

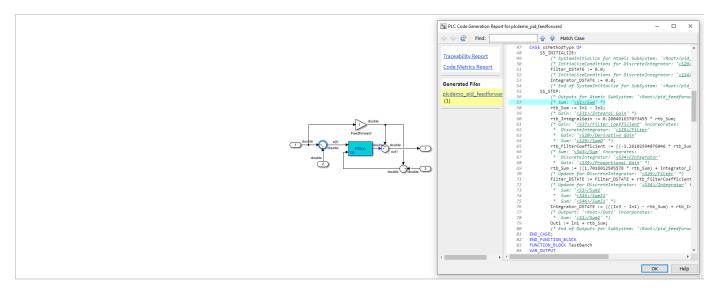

### **Code Traceability**

| Verify Generated Code by Using Code TracingTraceable ElementsTraceability in Generated CodeTraceability TagsOperator TraceabilityGenerate a Traceability Report from the Command LineTraceability Limitations | 6-2<br>6-3<br>6-5<br>6-5<br>6-6<br>6-6 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Trace Simulink Model Elements in Generated Code         Code-To-Model Traceability         Model-to-Code Traceability                                                                                         | 6-8<br>6-8<br>6-9                      |

| Trace Stateflow Elements in Generated Code            Inline Traceability for Stateflow Elements                                                                                                              | 6-11<br>6-11                           |

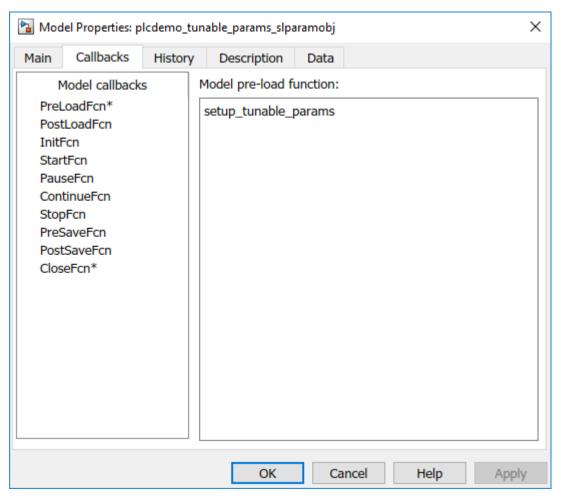

#### Working with Tunable Parameters in the Simulink PLC Coder Environment

| Block Parameters in Generated Code                                                                                                                                                            | 7-2                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Control Appearance of Block Parameters in Generated Code<br>Configure Tunable Parameters with Simulink.Parameter Objects<br>Make Parameters Tunable Using Configuration Parameters Dialog Box | 7-4<br>7-4<br>7-6               |

| Controlling Generated Code Partiti                                                                                                                                                            | ons                             |

| Generate Global Variables from Signals in Model                                                                                                                                               | 8-2                             |

| Control Code Partitions for Subsystem Block                                                                                                                                                   | 8-3<br>8-3<br>8-5<br>8-5<br>8-6 |

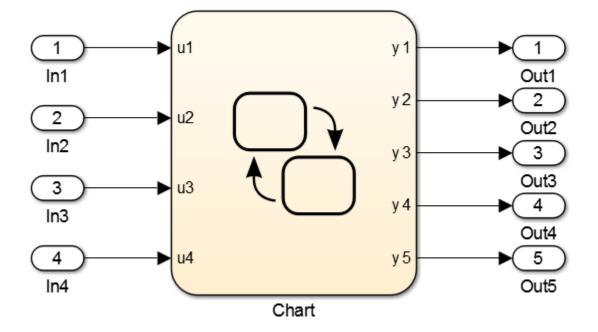

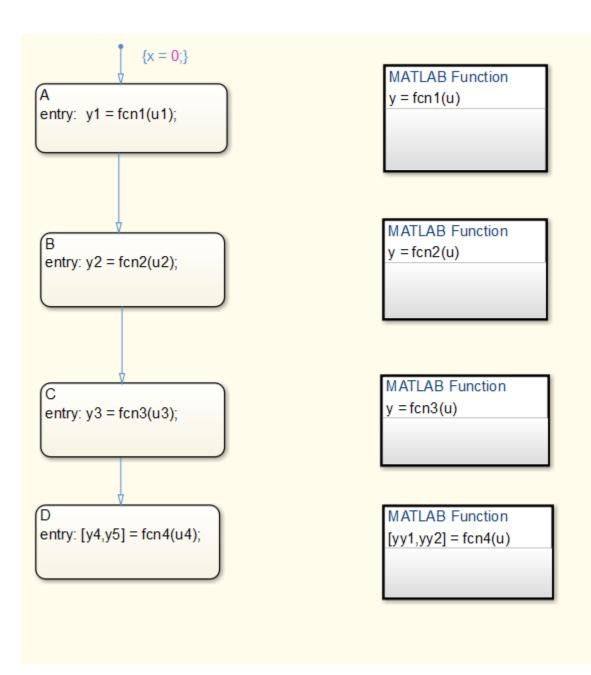

| Control Code Partitions for MATLAB Functions in Stateflow Charts                                                                                                                              | 8-8                             |

| Integrating Externally Defined Identif                                                                                                                                                        | ìers                            |

| Integrate Externally Defined Identifiers                                                                                                                                                      | 9-2                             |

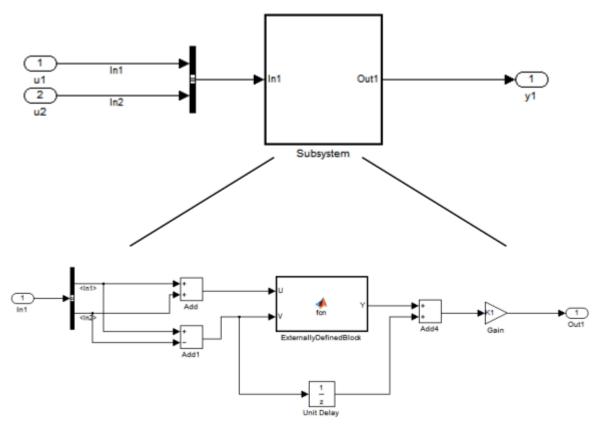

| Integrate Custom Function Block in Generated Code                                                                                                                                             | 9-3                             |

#### **IDE-Specific Considerations**

# Integrate Generated Code with Siemens IDE Project 10-2 Integrate Generated Code with Siemens SIMATIC STEP 7 Projects 10-2 Integrate Generated Code with Siemens TIA Portal Projects 10-2 Use Internal Signals for Debugging in RSLogix 5000 IDE 10-3

| Rockwell Automation RSLogix Requirements   | 10-4                                         |

|--------------------------------------------|----------------------------------------------|

| Add-On Instruction and Function Blocks     | 10-4                                         |

| Double-Precision Data Types                | 10-4                                         |

| Unsigned Integer Data Types                | 10-4                                         |

| Unsigned Fixed-Point Data Types            | 10-4                                         |

| Enumerated Data Types                      | 10-4                                         |

| Reserved Keywords                          | 10-4                                         |

| Rockwell Automation IDE selection          | 10-5                                         |

| Siemens IDE Requirements                   | 10-6<br>10-6<br>10-6<br>10-7<br>10-7<br>10-7 |

| Selectron CAP1131 IDE Requirements         | 10-8                                         |

| Double-Precision Floating-Point Data Types | 10-8                                         |

| Enumerated Data Types                      | 10-8                                         |

## 11

12

#### Supported Simulink and Stateflow Blocks

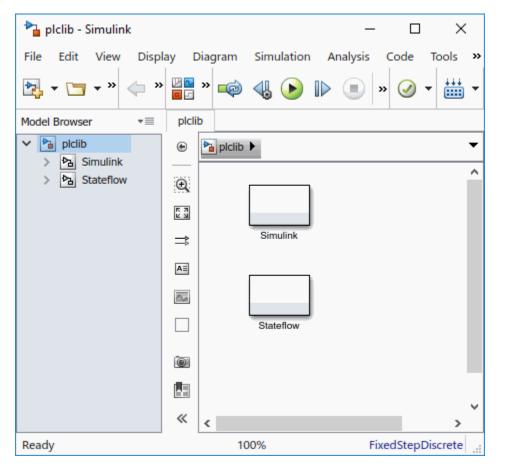

| Supported Blocks               | 11-2 |

|--------------------------------|------|

| View Supported Blocks Library  | 11-2 |

| Supported Simulink Blocks      | 11-2 |

| Supported Stateflow Blocks     | 11-9 |

| Blocks with Restricted Support | 11-9 |

#### Limitations

#### Structured Text Code Generation Limitations 12-2 General Limitations 12-2 12-3 Restrictions ..... Negative Zero 12-3 Divide by Zero 12-3Fixed-Point Data Type Multiword Operations ..... 12-3 Inplace Variables Code Generation 12-3 Simulink Data Dictionary 12-4 Ladder Logic Code Generation Limitations ..... 12-5 plcladderlib Limitations 12-5Ladder Diagram Import Limitations 12-5Ladder Diagram Modeling and Simulation Limitations ..... 12-5 Ladder Diagram Code Generation Limitations 12-5Ladder Diagram Verification Limitations 12-6

| 1 | 2 |

|---|---|

| ┻ | 5 |

| PLC Coder: General                                                                   | 13-2           |

|--------------------------------------------------------------------------------------|----------------|

| PLC Coder: General Tab Overview                                                      | 13-3           |

| Target IDE                                                                           | 13-3           |

| Show Full Target List                                                                | 13-5           |

| Target IDE Path                                                                      | 13-6           |

| Code Output Directory                                                                | 13-7           |

| Generate Testbench for Subsystem                                                     | 13-7<br>13-8   |

| Include Testbench Diagnostic Code       Generate Functions Instead of Function Block | 13-8           |

| Allow Functions with Zero Inputs                                                     | 13-0           |

| Suppress Auto-Generated Data Types                                                   | 13-10          |

| Emit Data type Worksheet Tags for PCWorx                                             | 13-10          |

| Aggressively Inline Structured Text Function Calls                                   | 13-11          |

| Signal Builder Block Time Range to Generate Multi Testbench                          | 13-12          |

| Enable unsigned integer and double datatypes in generated code                       | 13-12          |

| Allow nesting of UDTs if fields are more than allowed threshold                      | 13-13          |

| Maximum number of fields allowed in a UDT                                            | 13-13          |

|                                                                                      |                |

| PLC Coder: Comments                                                                  | 13-15          |

| Comments Overview                                                                    | 13-15          |

| Include Comments                                                                     | 13-15          |

| Include Block Description                                                            | 13-16          |

| Simulink Block / Stateflow Object Comments                                           | 13-17          |

| Show Eliminated Blocks                                                               | 13-17          |

|                                                                                      |                |

| PLC Coder: Optimization                                                              | 13-19          |

| Optimization Overview                                                                | 13-19          |

| Default Parameter Behavior                                                           | 13-20<br>13-21 |

| Signal Storage Reuse                                                                 | 13-21          |

| Of-Range Values                                                                      | 13-22          |

| Generate Reusable Code                                                               | 13-22          |

| Inline Named Constants                                                               | 13-23          |

| Reuse MATLAB Function Block Variables                                                | 13-24          |

| Fold temporary variable using function block instance output variable .              | 13-24          |

| Loop Unrolling Threshold                                                             | 13-25          |

| Remove unused ssmethod FB call arguments                                             | 13-26          |

|                                                                                      |                |

| PLC Coder: Identifiers                                                               | 13-27          |

| Identifiers Overview                                                                 | 13-28          |

| Use Subsystem Instance Name as Function Block Instance Name                          | 13-28          |

| Override Target Default Maximum Identifier Length                                    | 13-28          |

| Maximum Identifier Length                                                            | 13-29          |

| Override Target Default enum Name Behavior                                           | 13-30          |

| Generate enum Cast Function                                                          | 13-30          |

| Use the Same Reserved Names as Simulation Target                                     | 13-31          |

| Reserved Names                                                                       | 13-31          |

| Externally Defined Identifiers                                                       | 13-32          |

| Preserve Alias Type Names for Data Types                                             | 13-32<br>13-33 |

| Inline Enum Cast Function                                                            | 10-00          |

| PLC Coder: Report                                                       | 13-35 |

|-------------------------------------------------------------------------|-------|

| Report Overview                                                         | 13-35 |

| Generate Traceability Report                                            | 13-36 |

| Generate Model Web View                                                 | 13-36 |

| Open Report Automatically                                               | 13-37 |

| PLC Coder:Interface                                                     | 13-38 |

| Interface Overview                                                      | 13-39 |

| Generate Logging Code                                                   | 13-39 |

| Keep Top-Level ssmethod Name the Same as the Non-Top Level Name         |       |

| · · ·                                                                   | 13-39 |

| Remove Top-level Subsystem Ssmethod Type                                | 13-40 |

| Remove Initialization Statements for Externally Defined State Variables |       |

| · · · · · · · · · · · · · · · · · · ·                                   | 13-41 |

| Absolute-Time Temporal Logic                                            | 13-41 |

| Exclude block definitions as Functions                                  | 13-42 |

| Exclude block definitions as Function blocks                            | 13-43 |

| Use output argument syntax in function and function block calls         | 13-43 |

|                                                                         |       |

#### **External Mode**

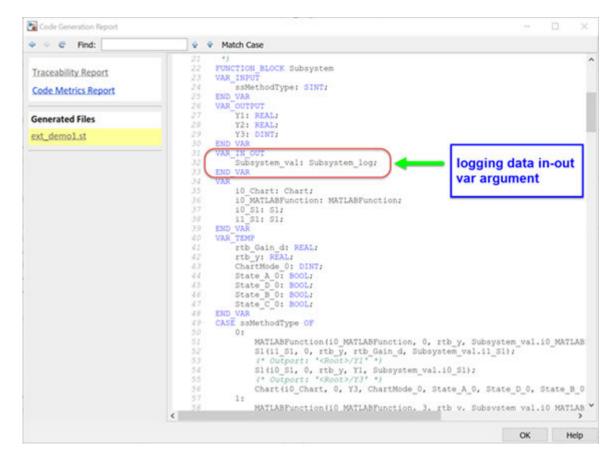

| External Mode Logging                                                   | 14-2 |

|-------------------------------------------------------------------------|------|

| Generate Structured Text Code That Has Logging Instrumentation $\ldots$ | 14-3 |

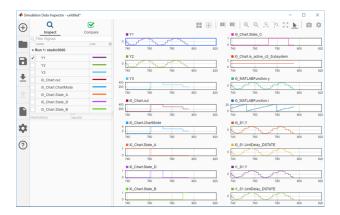

| Visualize and Monitor Logging Data by using Simulation Data Inspector   |      |

|                                                                         | 14-7 |

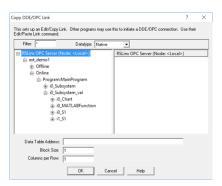

| Set Up and Download Code to Studio 5000 IDE                             | 14-7 |

| Configure RSLinx OPC Server                                             | 14-8 |

| Stream and Display Live Log Data by Using PLC External Mode Commands    |      |

|                                                                         | 14-8 |

#### Ladder Diagram Instructions

| Instructions Supported in Ladder Diagram 15- |

|----------------------------------------------|

|----------------------------------------------|

#### Ladder Diagram Blocks

|  | 1 | -6 |  |

|--|---|----|--|

|--|---|----|--|

15

| Ladder Diagram Blocks |  | 16-2 |

|-----------------------|--|------|

|-----------------------|--|------|

# **17**

| Block Parameters | 17-2 |

|------------------|------|

| Model Parameters | 17-3 |

| Limitations      | 17-4 |

#### **Generating PLC Code for Multirate Models**

## **18**

| Multirate Model Requirements for PLC Code Generation | 18-2 |

|------------------------------------------------------|------|

| Model Configuration Parameters                       | 18-2 |

| Limitations                                          | 18-2 |

#### **Generating PLC Code for MATLAB Function Block**

# **19**

| Configuring the rand function for PLC Code generation | 19-2 |

|-------------------------------------------------------|------|

| Width block requirements for PLC Code generation      | 19-3 |

| Workspace Parameter Data Type Limitations             | 19-4 |

| Limitations                                           | 19-5 |

#### **Model Architecture and Design**

| Fixed Point Simulink PLC Coder Structured Text Code Generation   |

|------------------------------------------------------------------|

| Block Parameters                                                 |

| Model Parameters                                                 |

| Limitations                                                      |

| Generating Simulink PLC Coder Structured Text Code for Multirate |

| Models                                                           |

| Multirate Model Requirements for PLC Code Generation             |

|                                                                  |

| MATLAB Function Block Simulink PLC Coder Structured Text Code    |

| Generation                                                       |

| Configuring the rand function for PLC Code Generation            |

| Simulink Width Block Requirements for PLC Code generation        |

| Workspace Parameter Data Type Limitations                        |

| Limitations                                                      |

| Deploy Structured Text                            | 2        |

|---------------------------------------------------|----------|

| Learning Objectives                               |          |

| Prerequisites                                     |          |

| Workflow                                          |          |

| Importing Generated Structured Text Code Manually |          |

|                                                   |          |

| Deploy Ladder Diagram                             | 2        |

| Learning Objectives                               |          |

|                                                   |          |

|                                                   |          |

| Prerequisites                                     | <b>2</b> |

#### Simulink PLC Coder Structured Text Code Generation For Simulink Data Dictionary (SLDD)

## 22

| Generate Structured Text Code For Simulink Data Dictionary Defined |

|--------------------------------------------------------------------|

| Model Parameters                                                   |

| Learning Objectives                                                |

| Requirements                                                       |

| Workflow                                                           |

#### Simulink PLC Coder Structured Text Code Generation For Enumerated Data Type

## 23

Structured Text Code Generation for Enum To Integer Conversion .... 23-2

#### **Distributed Code Generation with Simulink PLC Coder**

| Distributed Model Code Generation Options                         | 24-2  |

|-------------------------------------------------------------------|-------|

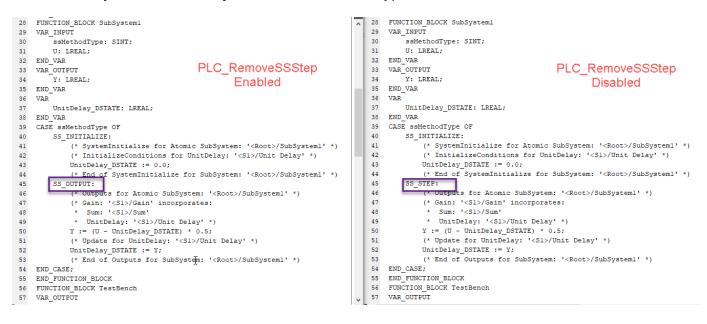

| Generated Code Structure for PLC_RemoveSSStep                     | 24-3  |

| Generated Code Structure for PLC_PreventExternalVarInitialization | 24-5  |

| PLC_RemoveSSStep for Distributed Code Generation                  | 24-7  |

| Structured Text Code Generation for Subsystem Reference Blocks    | 24-10 |

| Generate Structured Text Code for a Simple Simulink Subsystem                                                | 25-3  |

|--------------------------------------------------------------------------------------------------------------|-------|

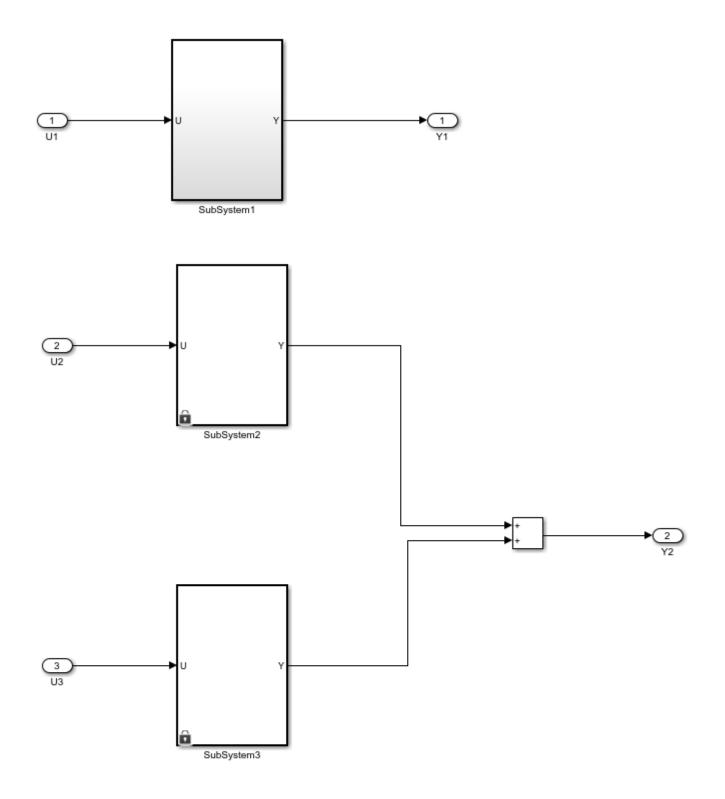

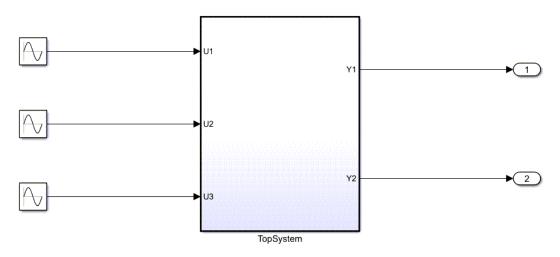

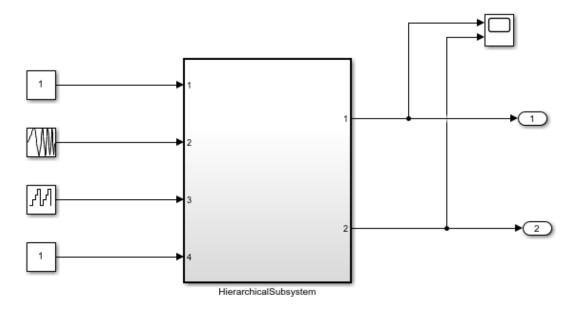

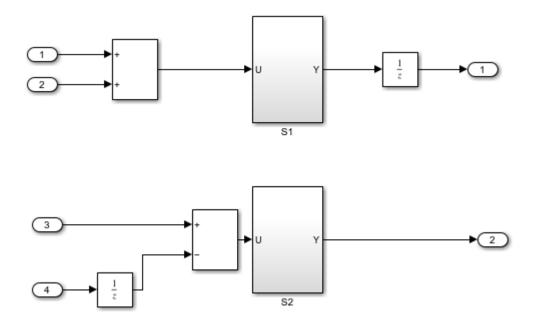

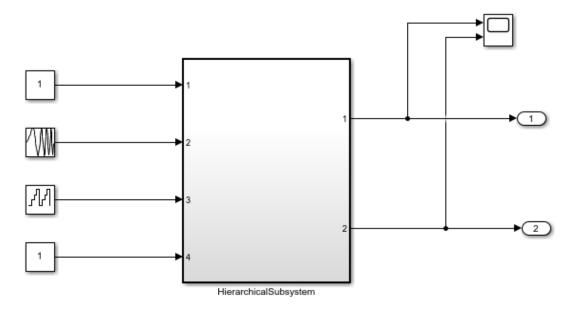

| Generating Structured Text for a Hierarchical Simulink Subsystem with<br>Virtual Subsystems                  | 25-8  |

| Generating Structured Text for a Hierarchical Simulink Subsystem $\ldots$                                    | 25-10 |

| Generate Structured Text Code for Reusable Subsystems                                                        | 25-12 |

| Generate Structured Text Code for a Simulink Subsystem that Has<br>Multirate Components                      | 25-15 |

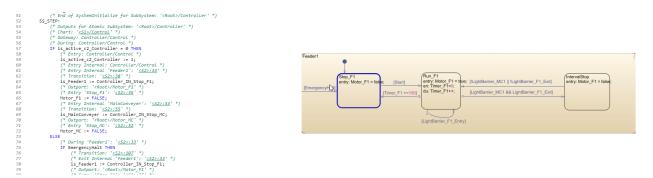

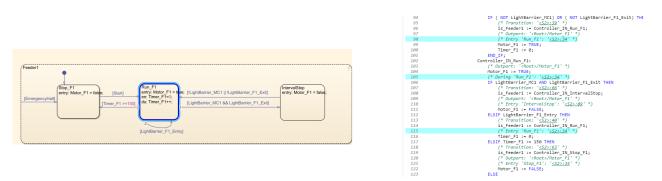

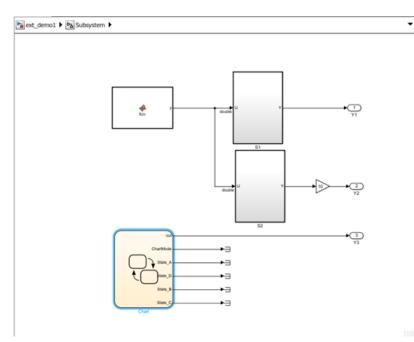

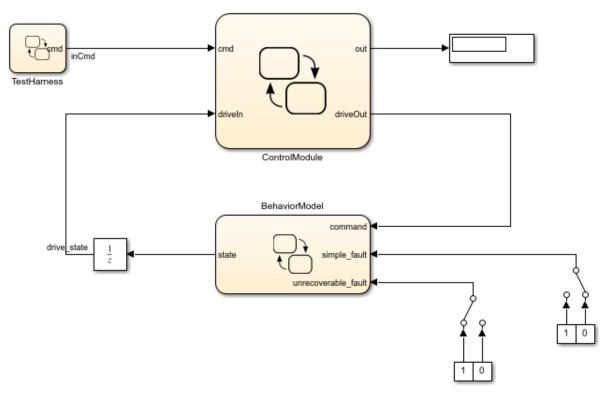

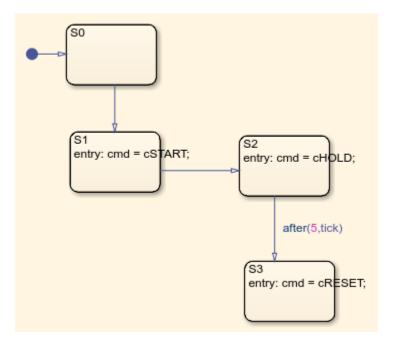

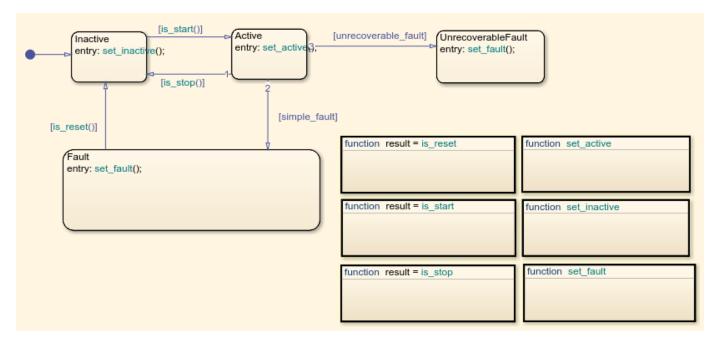

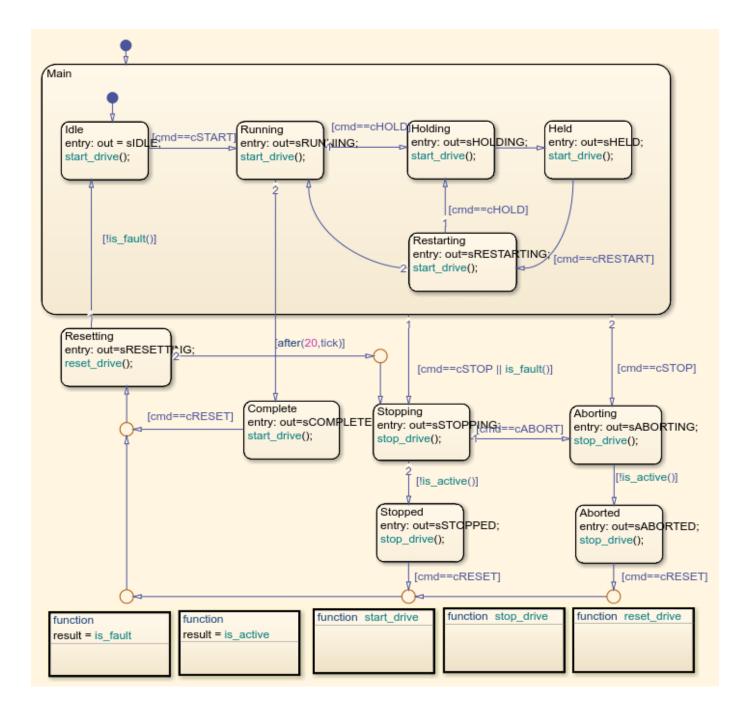

| Simulate and Generate Structured Text Code for a Stateflow Chart $\ldots$                                    | 25-20 |

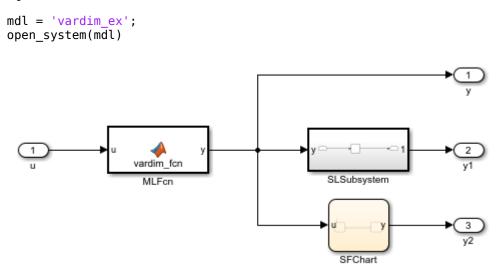

| Generate Structured Text Code for a MATLAB Function Block                                                    | 25-24 |

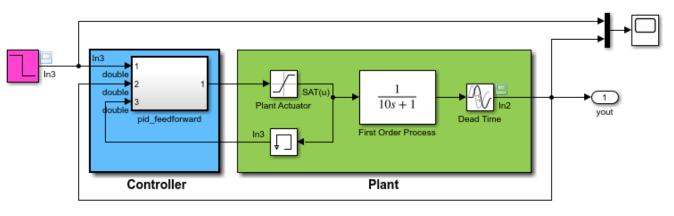

| Generating Structured Text for a Feedforward PID Controller                                                  | 25-26 |

| Mapping Tunable Parameters to Structured Text                                                                | 25-28 |

| Simulation and Code Generation for Tunable Parameters                                                        | 25-30 |

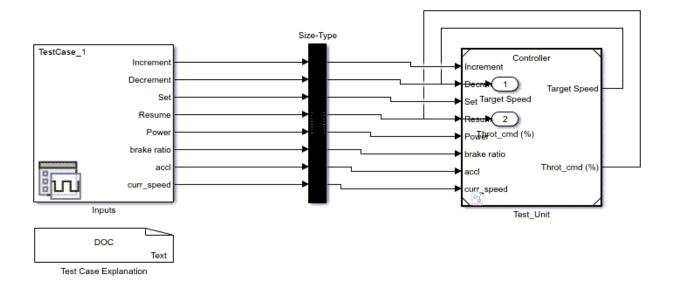

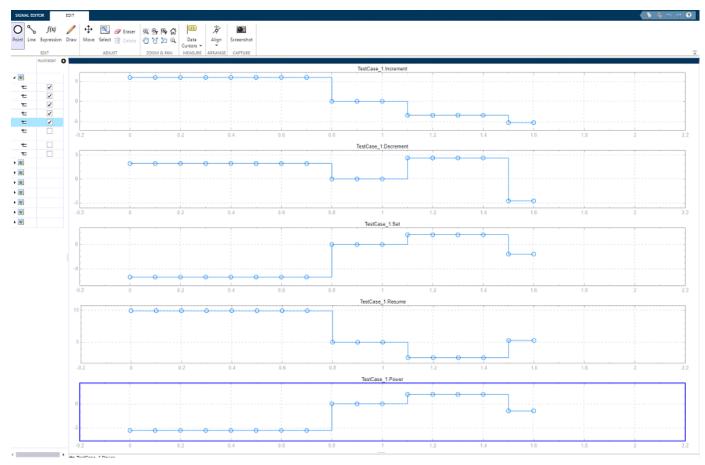

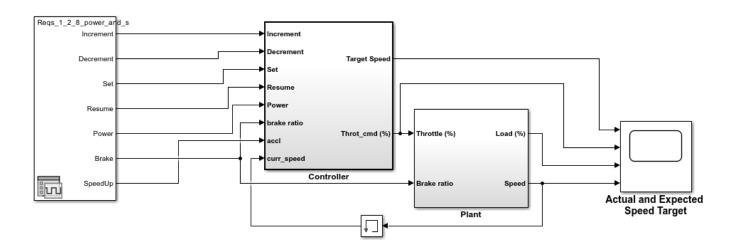

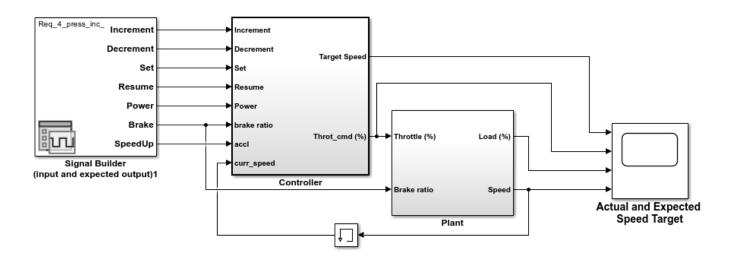

| Simulate and Generate Code for Speed Cruise Control System                                                   | 25-34 |

| Variable Step Speed Cruise Control System                                                                    | 25-36 |

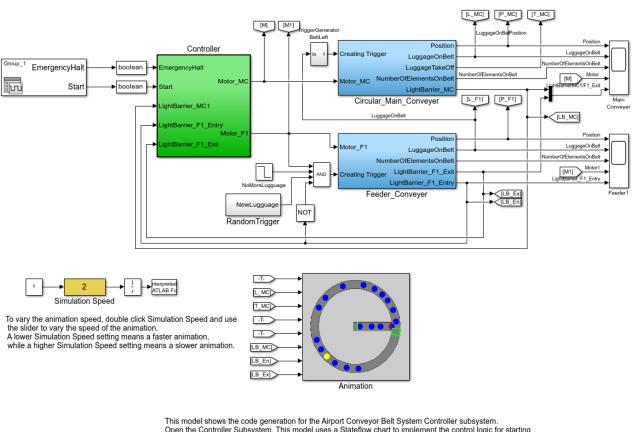

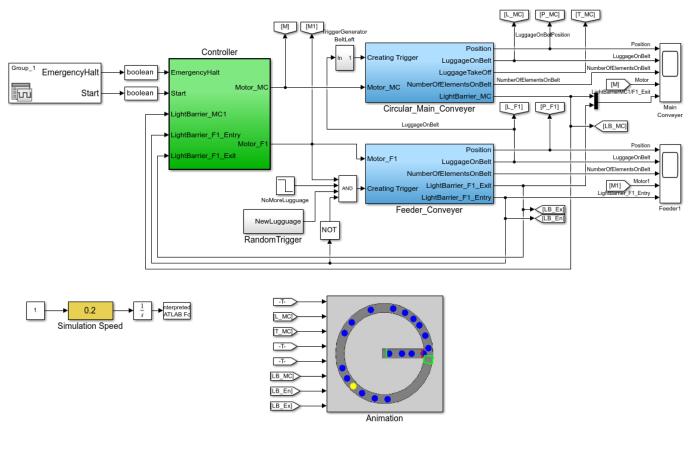

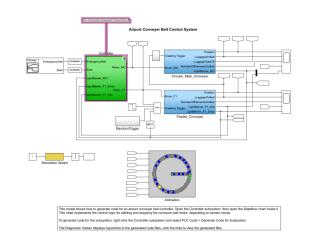

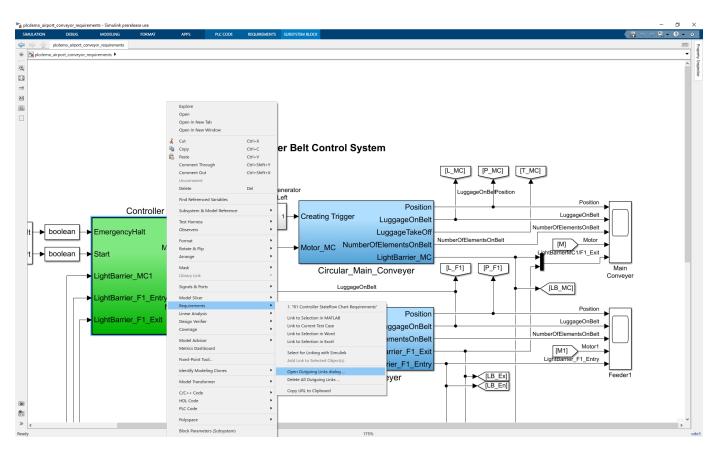

| Simulate and Generate Code for Airport Conveyor Belt Control System                                          | 25-38 |

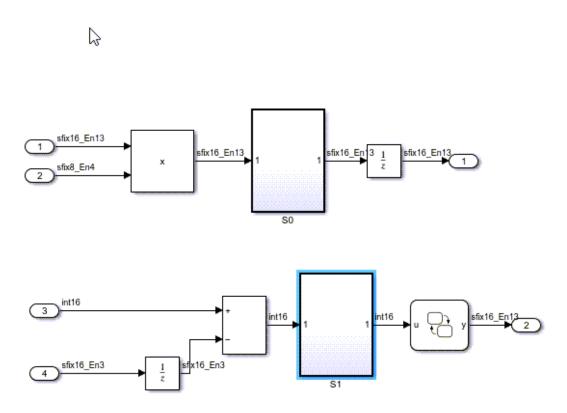

| Generate Structured Text Code for Simulink Model That Has Fixed-Point<br>Data Types                          | 25-39 |

| Generate Structured Text Code for a Stateflow Chart That Uses Absolute<br>Time Temporal Logic                | 25-41 |

| Integrating User Defined Function Blocks, Data Types, and Global<br>Variables into Generated Structured Text | 25-44 |

| Simulate and Generate Structured Text Code for Rockwell Automation<br>Motion Instructions                    | 25-46 |

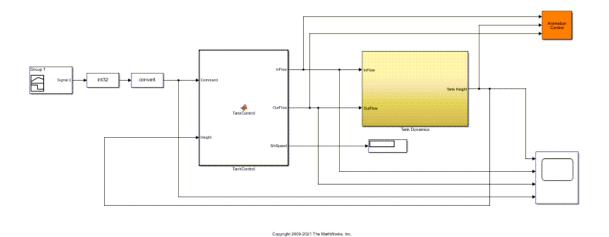

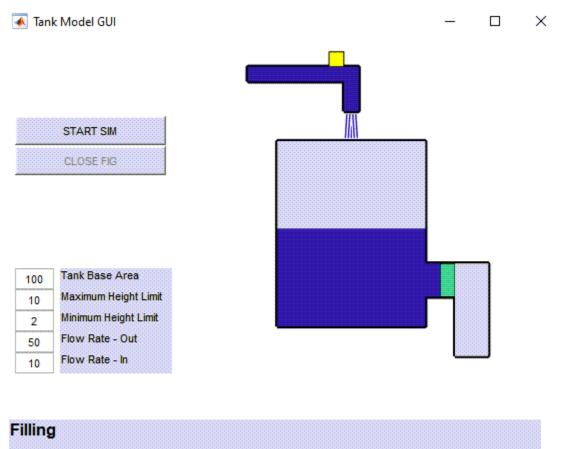

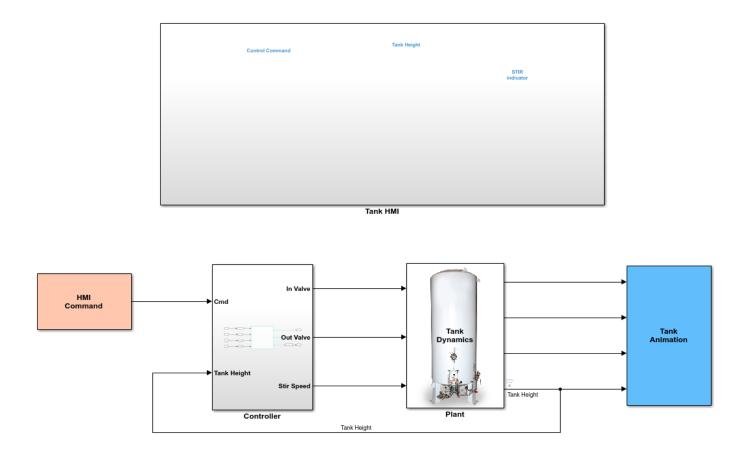

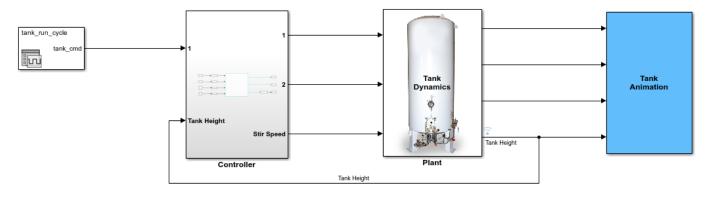

| Tank Control Simulation and Code Generation by Using Ladder Logic                                            | 25-48 |

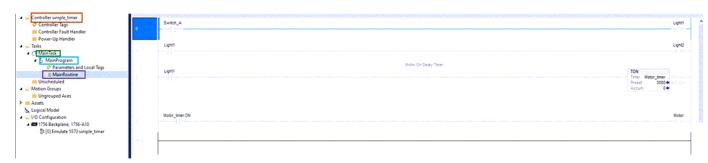

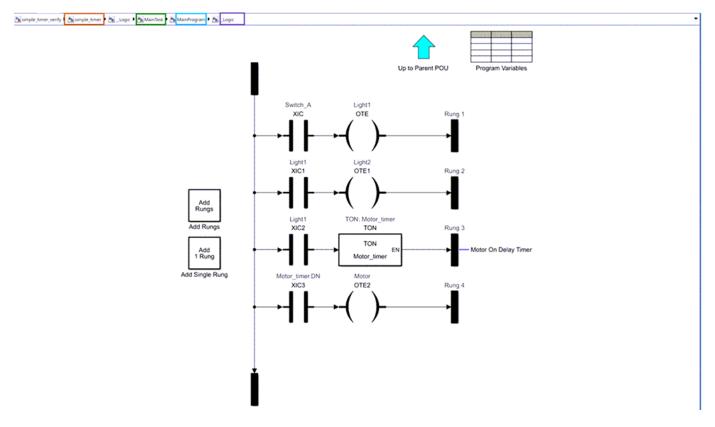

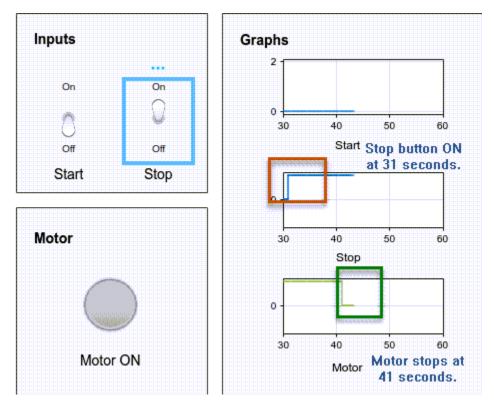

| Simulate, Model, and Generate Code for Timer-Based Ladder Logic                                              | 25-40 |

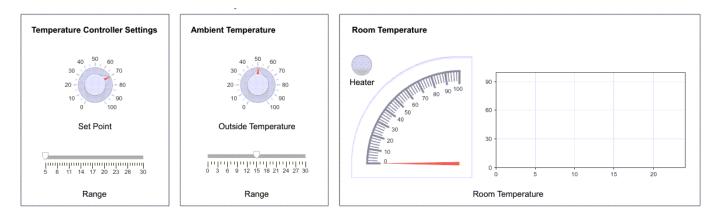

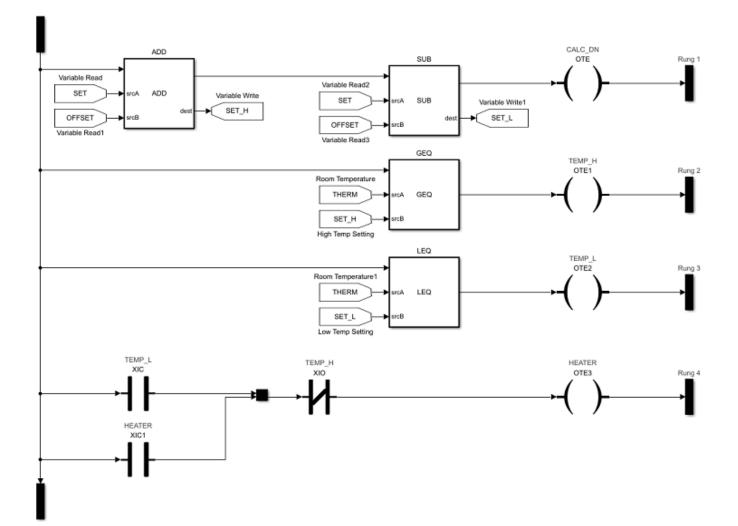

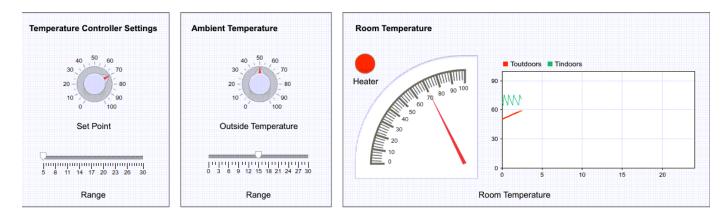

| Model, Simulate, and Generate Code for a Ladder Logic-Based<br>Temperature Controller                        | 25-57 |

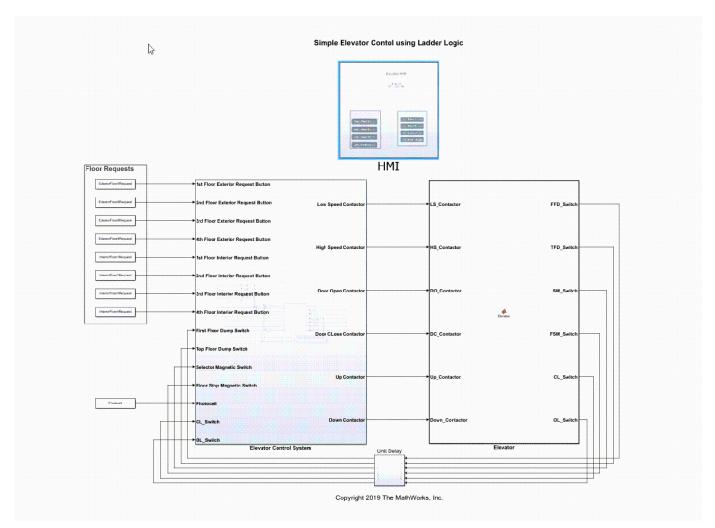

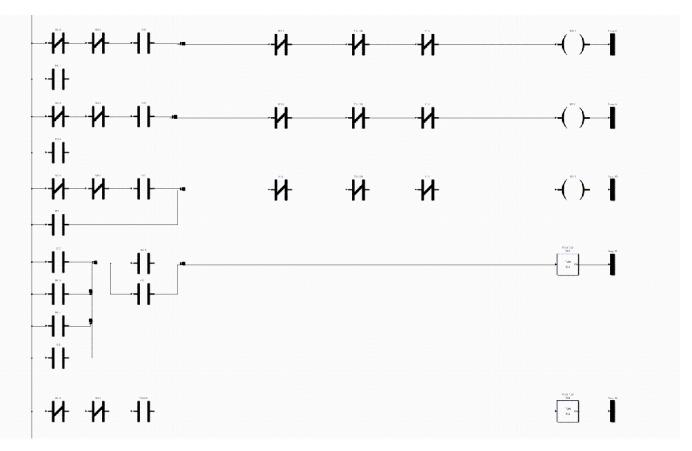

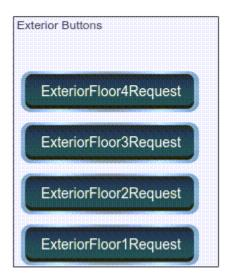

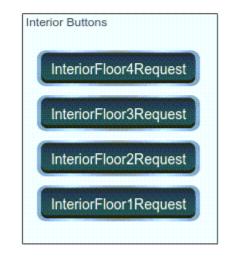

| Model, Simulate, and Generate Code for Ladder Logic-Based Elevator<br>Controller | 25-61      |

|----------------------------------------------------------------------------------|------------|

| Structured Text Code Generation for Simulink Data Dictionary                     | 25-67      |

| Structured Text Code Generation for Subsystem Reference Blocks $\ldots$          | 25-68      |

| PLC_RemoveSSStep for Distributed Code Generation                                 | 25-69      |

| Structured Text Code Generation for Enum To Integer Conversion $\ldots$          | 25-72      |

| Structured Text Code Generation for Integer To Enum Conversion $\ldots$          | 25-73      |

| Prevent External Variable Initialization for Distributed Code Generation         | 1<br>25-74 |

| Simulation and Structured Text Generation for MPC Controller Block               | 25-76      |

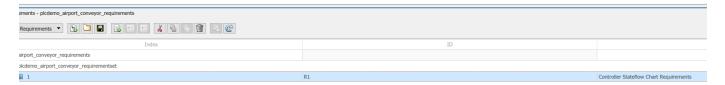

| View Requirement Links from Generated Code                                       | 25-80      |

| Run-Time Data Collection by Using External Mode Logging                          | 25-83      |

| Verify Generated Code by Using Cosimulation                                      | 25-87      |

| Generate Structured Text Code for Variable-Size Signals                          | 25-94      |

| Add Subsystem Port and Bus Descriptions in Generated Code                        | 25-96      |

| Generate Structured Text Code By Using a Custom Supported Function<br>List       | 25-99      |

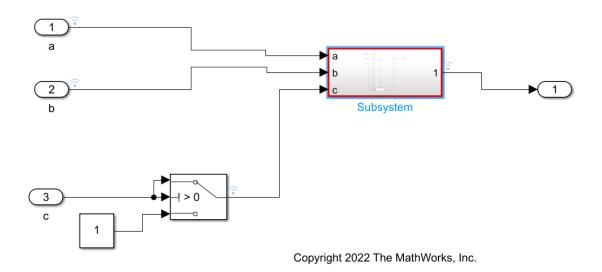

| Generate Optimized Structured Text Code by Folding Expressions $\dots$           | 25-101     |

| Generate Structured Text Code with VAR_IN_OUT Variables                          | 25-104     |

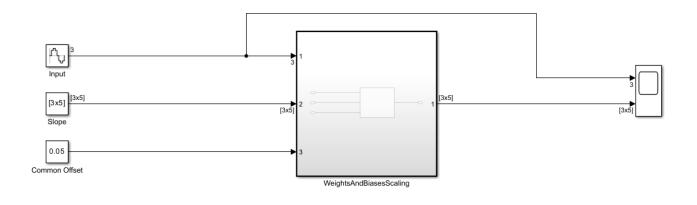

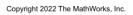

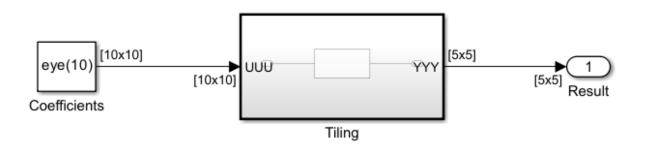

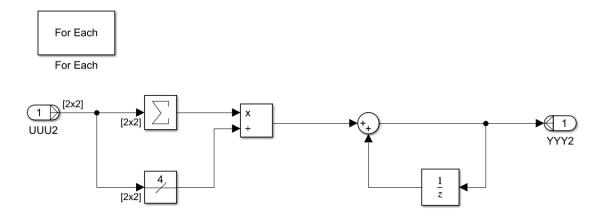

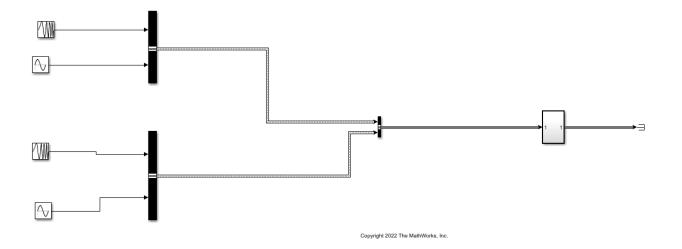

| Generate Structured Text Code from For Each Subsystems                           | 25-107     |

| Generate Structured Text Code for Width Blocks                                   | 25-110     |

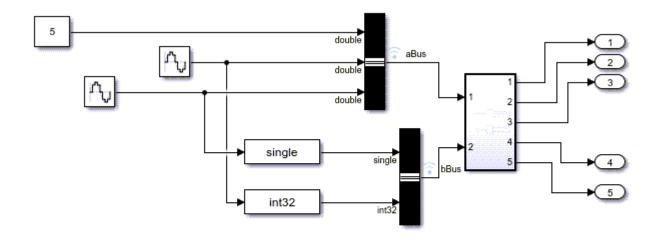

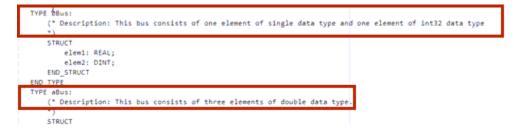

| Generate Bus Variables as STRUCT Data Types in Structured Text Code              | 25-112     |

#### PLC Coder Model Advisor

| PLC Coder Checks in Model Advisor Overview |      |

|--------------------------------------------|------|

| Model Configuration Checks                 | 26-3 |

| Check Data Store Memory blocks                    | 26-4           |

|---------------------------------------------------|----------------|

| Description                                       | 26-4           |

| Results and Recommended Actions                   | 26-4           |

| Capabilities and Limitations                      | 26-4           |

|                                                   |                |

| Check model for Stateflow messages                | 26-5           |

| Description                                       | 26-5           |

| Results and Recommended Actions                   | 26-5           |

| Capabilities and Limitations                      | 26-5           |

|                                                   |                |

| Check if signal lines are configured properly     | 26-6           |

| Description                                       | 26-6           |

| Results and Recommended Actions                   | 26-6           |

| Capabilities and Limitations                      | 26-6           |

|                                                   |                |

| Check if model uses row-major algorithms          | 26-7           |

| Description                                       | 26-7           |

| Results and Recommended Actions                   | 26-7           |

| Capabilities and Limitations                      | 26-7           |

|                                                   |                |

| Check model mask parameters                       | 26-8           |

| Description                                       | 26-8           |

| Results and Recommended Actions                   | 26-8           |

| Capabilities and Limitations                      | 26-8           |

| •                                                 |                |

| Check if model uses custom code                   | 26-9           |

| Description                                       | 26-9           |

| Results and Recommended Actions                   | 26-9           |

| Capabilities and Limitations                      | 26-9           |

|                                                   |                |

| Check model tunable parameters                    | 26-10          |

| Description                                       | 26-10          |

| Results and Recommended Actions                   | 26-10          |

| Capabilities and Limitations                      | 26-10          |

|                                                   | -0 10          |

| Check for blocks and block settings overview      | 26-11          |

| check for blocks and block settings overview      | 20 11          |

| Check if model uses event based blocks            | 26-12          |

| Description                                       | 26-12          |

| Results and Recommended Actions                   | 26-12          |

| Capabilities and Limitations                      | 26-12          |

|                                                   | 20-12          |

| Check if model uses probe blocks                  | 26-13          |

| Description                                       | 26-13          |

| Results and Recommended Actions                   | 26-13          |

| Capabilities and Limitations                      | 26-13          |

|                                                   | 20-15          |

| Check if model uses environment controller blocks | 26-14          |

|                                                   | 20-14<br>26-14 |

| Description                                       | 20-14<br>26-14 |

|                                                   | 20-14<br>26-14 |

| Capabilities and Limitations                      | 20-14          |

| Check Stateflow chart undate                      | 26-15          |

| Check Stateflow chart update                      | 20-15<br>26-15 |

| Description                                       | 20-15<br>26-15 |

| Neouro anu Neconniciaeu Acronio                   | 40-1J          |

| Capabilities and Limitations                                        | 26-15                        |

|---------------------------------------------------------------------|------------------------------|

| Check issues with integrator blocks                                 | 26-16                        |

| Description                                                         | 26-16                        |

| Results and Recommended Actions                                     | 26-16                        |

|                                                                     | <b>26-10</b><br><b>26-16</b> |

| Capabilities and Limitations                                        | 20-10                        |

| Check if model uses unsupported blocks                              | 26-17                        |

| Description                                                         | 26-17                        |

| Results and Recommended Actions                                     | 26-17                        |

| Capabilities and Limitations                                        | 26-17                        |

|                                                                     | 00.40                        |

| Check if model can generate testbench                               | 26-18                        |

| Description                                                         | 26-18                        |

| Results and Recommended Actions                                     | 26-18                        |

| Capabilities and Limitations                                        | 26-18                        |

| Check function packaging configuration                              | 26-19                        |

|                                                                     | <b>26-19</b>                 |

| Description                                                         |                              |

| Results and Recommended Actions                                     | 26-19                        |

| Capabilities and Limitations                                        | 26-19                        |

| Check trigonometric blocks                                          | 26-20                        |

| Description                                                         | 26-20                        |

| Results and Recommended Actions                                     | 26-20                        |

|                                                                     | <b>26-20</b><br><b>26-20</b> |

| Capabilities and Limitations                                        | 20-20                        |

| Industry standard checks overview                                   | 26-21                        |

| Define names to avoid                                               | 26-22                        |

| Description                                                         | 26-22                        |

| Results and Recommended Actions                                     | 26-22                        |

|                                                                     | -                            |

| Define use of case (capitals)                                       | 26-23                        |

| Description                                                         | 26-23                        |

| Input Parameters                                                    | 26-23                        |

| Results and Recommended Actions                                     | 26-23                        |

|                                                                     | 20-25                        |

| Define maximum variable name length                                 | 26-24                        |

| Description                                                         | 26-24                        |

| Input Parameters                                                    | 26-24                        |

| Results and Recommended Actions                                     | 26-24                        |

|                                                                     |                              |

| Comments must describe purpose of component                         | 26-25                        |

| Description                                                         | 26-25                        |

| Results and Recommended Actions                                     | 26-25                        |

| Avoid nested comments                                               | 26.20                        |

| Avoid nested comments                                               | 26-26                        |

| Description                                                         | 26-26                        |

| Results and Recommended Actions                                     | 26-26                        |

| Define maximum number of input/output/in-out variables of a Program |                              |

| Organization Unit (POU)                                             | 26-27                        |

| Description                                                         | 26-27                        |

|                                                                     | 26-27                        |

| Input Parameters                                                    | 20-2/                        |

| Results and Recommended Actions              | 26-27 |

|----------------------------------------------|-------|

| Define type prefixes for variables (if used) |       |

| Description                                  | 26-28 |

| Results and Recommended Actions              | 26-28 |

#### Using the PLC Coder Model Advisor

| PLC Model Advisor Checks             | 27-2 |

|--------------------------------------|------|

| Model configuration checks           | 27-2 |

| Checks for blocks and block settings | 27-3 |

| Industry standard checks             | 27-3 |

#### **Custom Keyword List**

# 28

29

27

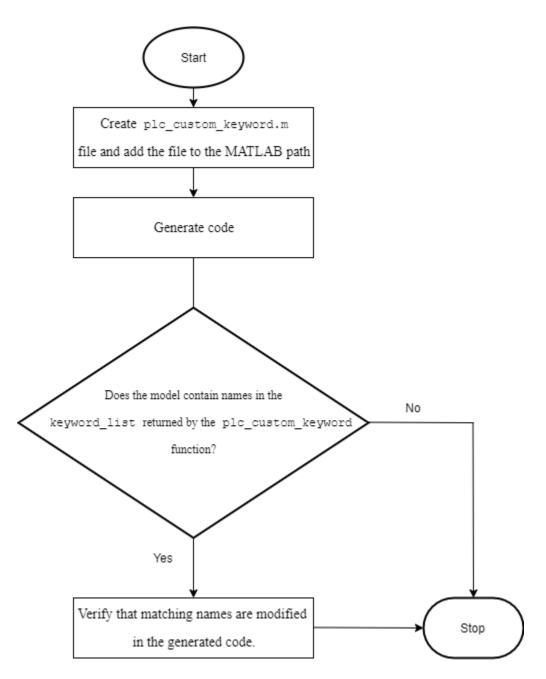

| Custom Keyword File Usage Workflow28-19Verify Custom Keyword Name Changes in Generated Code28-20 | Custom Keyword File Template       2         Custom Keyword File Usage Workflow       2         Verify Custom Keyword Name Changes in Generated Code       2 | 28-2<br>28-2<br>28-19<br>28-20<br>28-20<br>28-22 |

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

#### **Plugin Based Targets**

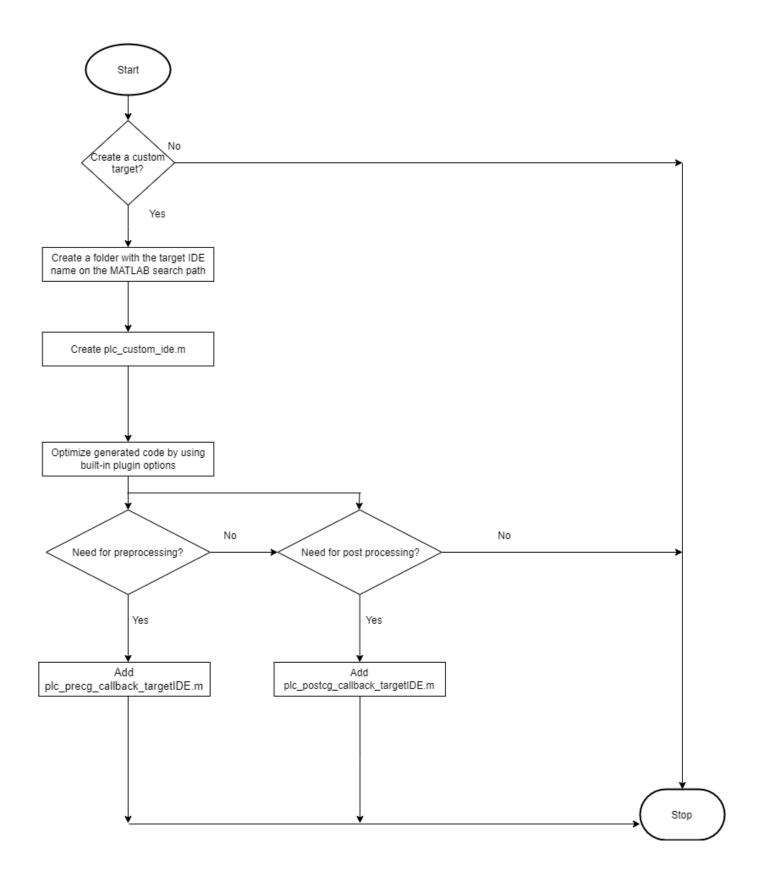

| Create Custom Target IDE for Code Generation                  | 29-2          |

|---------------------------------------------------------------|---------------|

| Plugin-Based Code Generation Workflow                         | 29-2          |

| Plugin Options                                                | <b>29-</b> 5  |

| Generate Code by Using Plugin-Based Target IDE                | <b>29-1</b> 5 |

| Generate Custom Code by Using IDE-Specific Callback Functions | 29-18         |

| Custom Code Generation Workflow                               | 29-18         |

| Create a Custom Callback Function                             | 29-18         |

| Generate Custom Code                                          | 29-20         |

#### Variable-Size Code Generation

| Variable-Size Signal Code Generation               | 30-2 |

|----------------------------------------------------|------|

| Limitations                                        | 30-2 |

| Variable-Size Code Generation Example              | 30-2 |

| Generated Code Structure for Variable-Size Signals | 30-2 |

# **Getting Started**

- "Simulink PLC Coder Product Description" on page 1-2

- "Prepare Model for Structured Text Generation" on page 1-3

- "Generate and Examine Structured Text Code" on page 1-7

- "Propagate Block Descriptions to Code Comments" on page 1-10

- "Files Generated by Simulink PLC Coder" on page 1-11

- "Specify Custom Names for Generated Files" on page 1-13

- "Import Structured Text Code Automatically" on page 1-14

- "Author, Manage, and Execute Simulation-Based Tests of Generated Code" on page 1-16

- "Simulation and Code Generation of Motion Instructions" on page 1-18

## Simulink PLC Coder Product Description

#### Generate IEC 61131-3 Structured Text and Ladder Diagrams for PLCs and PACs

Simulink PLC Coder generates hardware-independent IEC 61131-3 Structured Text and Ladder Diagrams from Simulink models, Stateflow<sup>®</sup> charts, and MATLAB<sup>®</sup> functions. Structured Text is generated in PLCopen XML and other file formats supported by widely used integrated development environments (IDEs) including CODESYS, Rockwell Automation<sup>®</sup> Studio 5000, Siemens<sup>®</sup> TIA Portal, and OMRON<sup>®</sup> Sysmac<sup>®</sup> Studio. Ladder diagrams are generated in file formats supported by Rockwell Automation Studio 5000. As a result, you can compile and deploy your application to numerous programmable logic controller (PLC) and programmable automation controller (PAC) devices.

Simulink PLC Coder generates test benches that help you verify the Structured Text and Ladder Diagrams using PLC and PAC IDEs and simulation tools. It also provides code generation reports with static code metrics and bidirectional traceability between model and code. Support for industry standards is available through IEC Certification Kit (for IEC 61508 and IEC 61511).

#### **Prepare Model for Structured Text Generation**

| In this | s section |

|---------|-----------|

|---------|-----------|

"Tasking Mode" on page 1-3

"Choose a Solver" on page 1-3

"Configure Simulink Models for Structured Text Code Generation" on page 1-3

"Verify System Compatibility for Structured Text Code Generation" on page 1-6

To generate structured text code from Simulink models, Stateflow charts, and MATLAB functions, use the Simulink PLC Coder product. Prepare your model for structured text code generation by performing action such as setting the solver, identifying if your model is a single rate or multirate model, and checking model compatibility for structured text code generation.

#### **Tasking Mode**

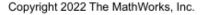

If your Simulink model contains multirate signals, you must set the tasking mode. If your Simulink model does not contain multirate signals, proceed to solver selection.

Simulink PLC Coder generates code for single-tasking subsystems. For multirate subsystems, you must first explicitly set the tasking mode to single-tasking before selecting a solver. In the model configuration, on the **Solver** pane, clear the check box for **Treat each discrete rate as a separate task**.

#### **Choose a Solver**

Choose a solver for your Simulink PLC Coder model.

| Model         | Solver Setting                                                                                        |

|---------------|-------------------------------------------------------------------------------------------------------|

| Variable-step | Use a continuous solver. Configure a fixed sample time for the subsystem for which you generate code. |

| Fixed-step    | Use a discrete fixed-step solver.                                                                     |

#### **Configure Simulink Models for Structured Text Code Generation**

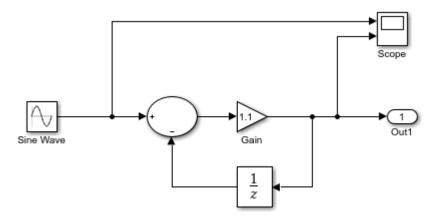

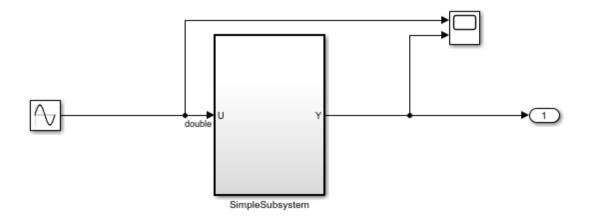

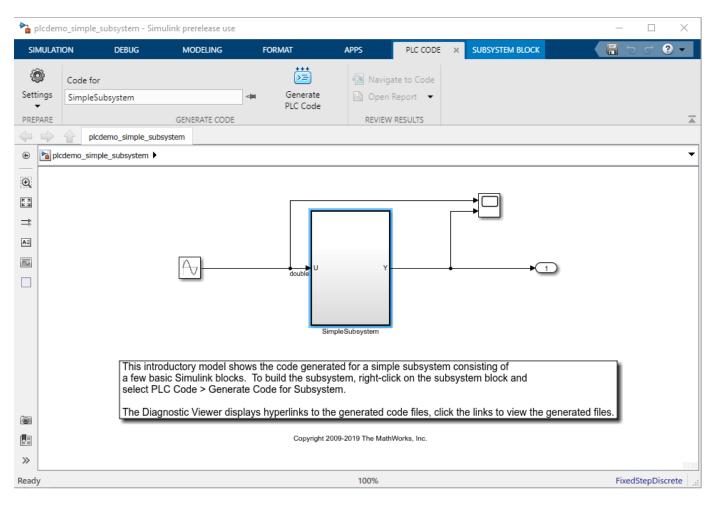

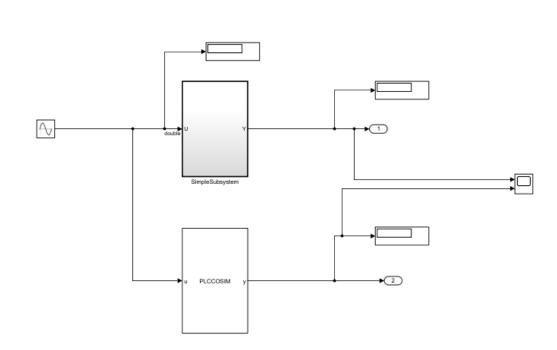

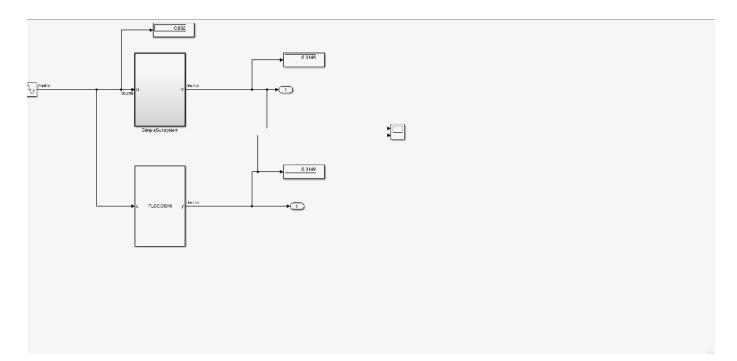

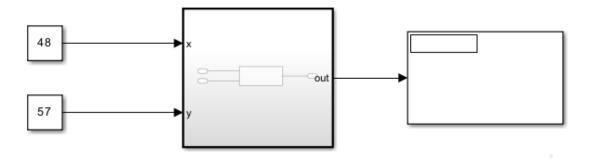

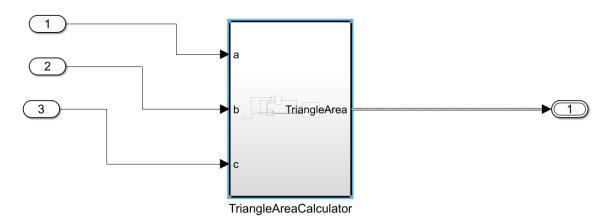

This tutorial uses the example model plcdemo\_simple\_subsyystem.

**1** In the Command Window, enter the model name to open the model.

plcdemo\_simple\_subsystem

2 Configure the model to use the fixed-step discrete solver. Click the solver link in the lower-right corner of the model window. In the Solver information pane, click View solver settings to open the Solver pane of the model configuration parameters. Under the Solver selection, set Type to Fixed-step and Solver to discrete (no continuous states).

If your model uses a continuous solver and has a subsystem, configure a fixed sample time for the subsystem for which you generate code.

- 3 Save this model as plcdemo\_simple\_subsystem1.

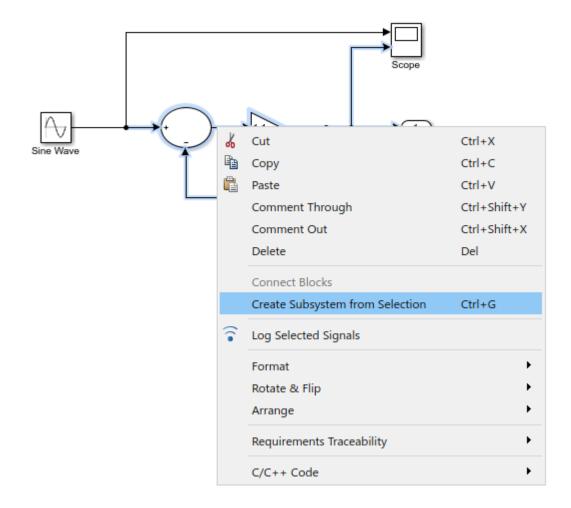

- **4** Create a subsystem containing the components for which you want to generate structured text code.

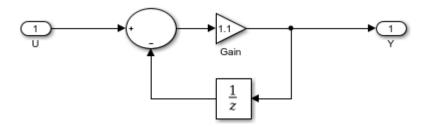

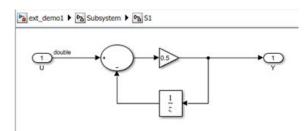

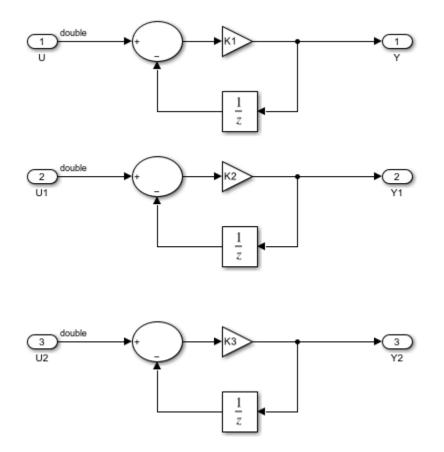

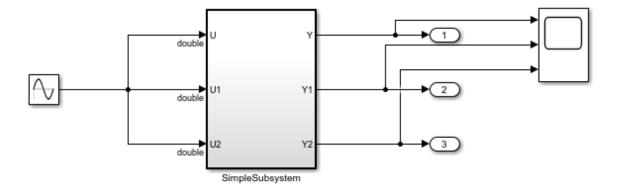

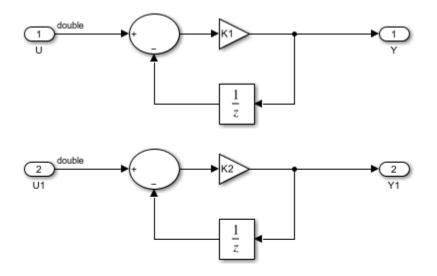

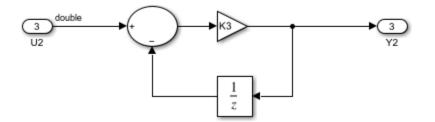

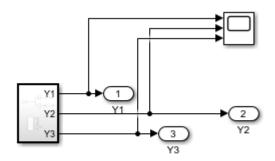

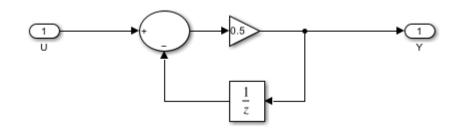

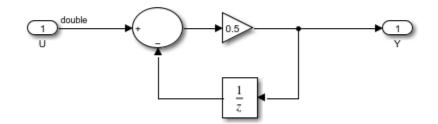

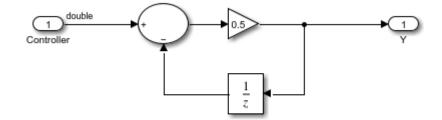

Optionally, rename In1 and Out1 to U and Y respectively, resulting in a subsystem like the following figure:

- **5** Save the model with the new subsystem.

- 6 In the top-level model, right-click the Subsystem block and select **Block Parameters** (Subsystem).

- 7 In the **Block Parameters** block dialog box, select **Treat as atomic unit**.

- 8 Click OK.

- **9** Simulate, and then save your model.

You can now:

- Set up your subsystem to generate structured text code. See "Verify System Compatibility for Structured Text Code Generation" on page 1-6.

- Generate structured text code for your IDE. See "Generate and Examine Structured Text Code" on page 1-7.

#### Verify System Compatibility for Structured Text Code Generation

You must already have a model configured to work with the Simulink PLC Coder software. If not, see "Prepare Model for Structured Text Generation" on page 1-3

- **1** In your model, navigate to the subsystem for which you want to generate code.

- 2 Right-click that subsystem block and select **PLC Code** > **Check Subsystem Compatibility**.

The coder verifies whether your model satisfies the Simulink PLC Coder criteria. When the verification is complete, a **View diagnostics** hyperlink appears at the bottom of the model window. Click this hyperlink to open the Diagnostic Viewer window.

If the subsystem is not atomic, right-click the subsystem block and select **PLC Code > Enable "Treat as atomic unit" to generate code**.

|                                                | signals or Forts             | , |                                                |

|------------------------------------------------|------------------------------|---|------------------------------------------------|

| U                                              | Requirements Traceability    | + |                                                |

|                                                | Linear Analysis              | + |                                                |

|                                                | Design Verifier              | + |                                                |

|                                                | Coverage                     | • |                                                |

|                                                | Model Advisor                | • |                                                |

|                                                | Fixed-Point Tool             |   |                                                |

|                                                | Model Transformer            | + |                                                |

|                                                | C/C++ Code                   | • |                                                |

|                                                | HDL Code                     | + |                                                |

| is the code generated<br>To build the subsyste | PLC Code                     | + | Enable "Treat as atomic unit" to generate code |

| Code for Subsystem.                            | Polyspace                    | • | Navigate to Code                               |

| ys hyperlinks to the g                         | Block Parameters (Subsystem) |   | erated files.                                  |

| Copyright 2009-                                | Properties                   |   |                                                |

|                                                | Help                         |   |                                                |

|                                                |                              |   |                                                |

In the block parameter dialog box, select **Treat as atomic unit**.

Generate structured text code for your IDE. See "Generate and Examine Structured Text Code" on page 1-7.

#### Generate and Examine Structured Text Code

#### In this section...

"Generate Structured Text from the Model Window" on page 1-7

"Generate Structured Text Through the MATLAB Interface" on page 1-7

"View Generated Code" on page 1-8

To generate structured text code from Simulink models, Stateflow charts, and MATLAB functions, use the Simulink PLC Coder product. Use the generated structured text code in applications such as rapid prototyping, control algorithm validation, and test bench verification.

#### **Generate Structured Text from the Model Window**

To generate structured text code from your Simulink model, complete the steps to prepare your model for structured text code generation. For more information, see "Prepare Model for Structured Text Generation" on page 1-3. This tutorial uses the plcdemo\_simple\_subsystem.

1 In the Command Window, enter the model name to open the model.

plcdemo\_simple\_subsystem

- 2 Open the **PLC Coder** app. Click the **PLC Code** tab.

- 3 Click **Settings**.

- 4 On the **PLC Code Generation** pane, select an option from the **Target IDE** list, for example, CODESYS 2.3.

The default **Target IDE** list displays the full set of supported IDEs. To see a reduced subset of the target IDEs supported by Simulink PLC Coder, clear the **Show full target list** check box. To customize this list, use the plccoderpref function.

- 5 Click OK.

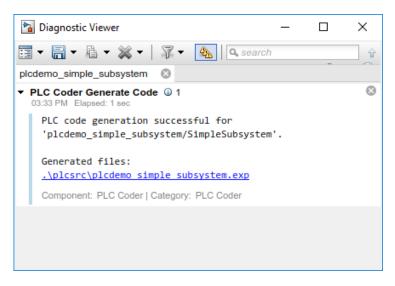

- 6 Click Generate PLC Code to:

- Generate structured text code.

- Store generated code in *model\_name*.exp (for example, plcdemo\_simple\_subsystem.exp)

When code generation is complete, a **View diagnostics** hyperlink appears at the bottom of the model window. Click this hyperlink to open the Diagnostic Viewer window.

This window has links that you can click to open the associated files. For more information, see "Files Generated by Simulink PLC Coder" on page 1-11.

#### Generate Structured Text Through the MATLAB Interface

You can generate structured text code for a subsystem in the Command Window by using the plcgeneratecode function. You must have already configured the parameters for the model or, alternatively, you can use the default settings.

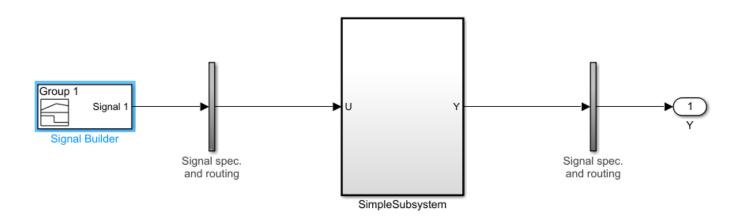

For example, to generate code from the SimpleSubsystem subsystem in the plcdemo\_simple\_subsystem model:

**1** Open the plcdemo\_simple\_subsystem model:

plcdemo\_simple\_subsystem

2 Open the Configuration Parameters dialog box by using the plcopenconfigset function:

plcopenconfigset('plcdemo\_simple\_subsystem/SimpleSubsystem')

- **3** Select a target IDE.

- 4 Configure the subsystem by preparing your model for structured text code generation. For more information, see "Prepare Model for Structured Text Generation" on page 1-3.

- **5** Generate code for the subsystem:

generatedfiles = plcgeneratecode('plcdemo\_simple\_subsystem/SimpleSubsystem')

When using plcgeneratecode for code generation, all diagnostic messages are printed to the MATLAB Command Window.

#### **View Generated Code**

After generating the code, you can view it in the MATLAB editor. For a description of how the generated code for the Simulink components map to structured text components, see "Verify Generated Code by Using Code Tracing" on page 6-2. You can view:

- Matrix data types: Simulink PLC Coder converts matrix data types to single-dimensional vectors (column-major) in the generated structured text.

- Generated code header: If your model has author names, creation dates, and model descriptions, the generated code contains these items in the header comments. The header also lists fundamental sample times for the model and the subsystem block for which you generate code.

- Code comments: You can choose to propagate block descriptions to comments in generated code. See "Propagate Block Descriptions to Code Comments" on page 1-10.

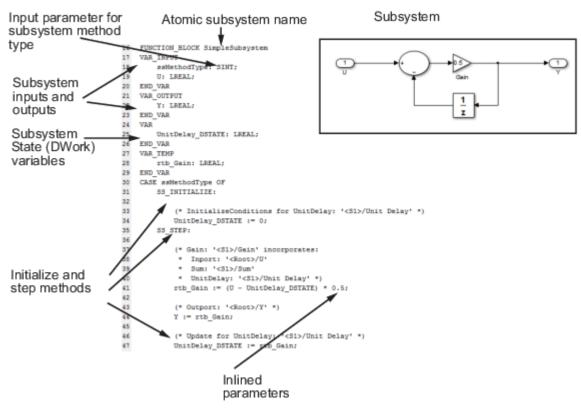

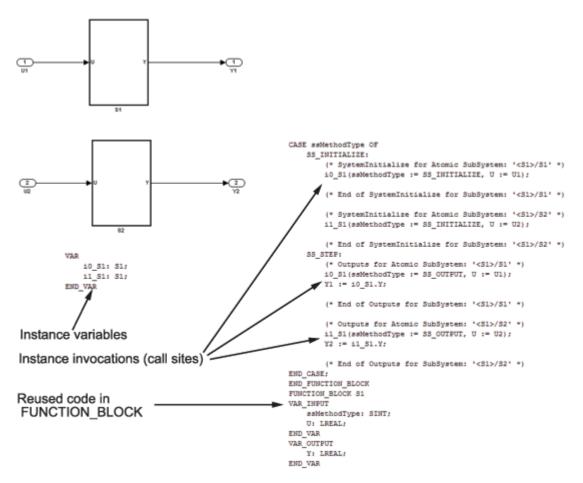

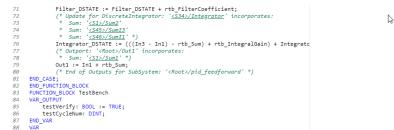

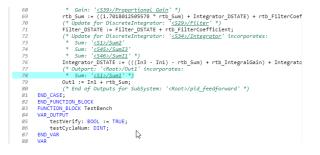

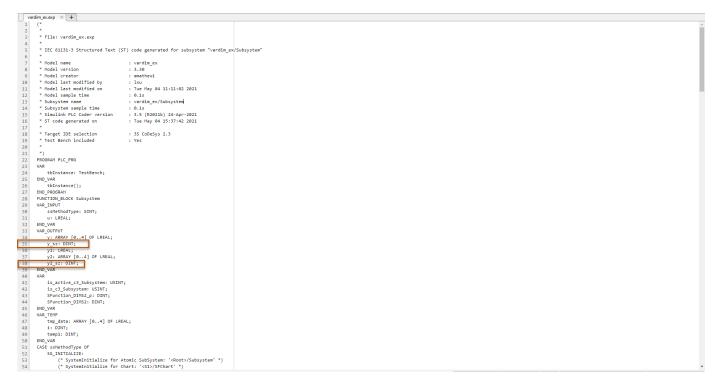

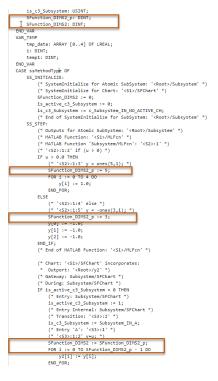

This figure illustrates generated code for the CODESYS Version 2.3 PLC IDE. Generated code for other platforms, such as Rockwell Automation RSLogix<sup>M</sup> 5000, is in XML or another format.

```

15

FUNCTION_BLOCK SimpleSubsystem

16

VAR_INPUT

17

ssMethodType: SINT;

18

U: LREAL;

19

END_VAR

VAR_OUTPUT

20

21

22

23

24

25

26

27

28

29

30

Y: LREAL;

END VAR

VAR

UnitDelay_DSTATE: LREAL;

END_VAR

VAR_TEMP

rtb_Gain: LREAL;

END VAR

CASE ssMethodType OF

SS_INITIALIZE:

31

(* InitializeConditions for UnitDelay: '<S1>/Unit Delay' *)

32

UnitDelay_DSTATE := 0;

33

34

35

37

38

39

40

41

42

43

44

45

SS_OUTPUT:

(* Gain: '<S1>/Gain' incorporates:

* Inport: '<Root>/U'

* Sum: '<S1>/Sum'

* UnitDelay: '<S1>/Unit Delay'

*)

rtb_Gain := (U - UnitDelay_DSTATE) * 0.5;

(* Outport: '<Root>/Y' *)

Y := rtb_Gain;

(* Update for UnitDelay: '<S1>/Unit Delay' *)

46

UnitDelay_DSTATE := rtb_Gain;

47

END_CASE;

48

49

END FUNCTION BLOCK

```

Once you are satisfied with the generated structured text code, optionally change your workflow to automatically generate and import code to the target IDE. For more information, see "Import Structured Text Code Automatically" on page 1-14.

## **Propagate Block Descriptions to Code Comments**

You can propagate block descriptions from the model to comments in your generated code.

For specific IDEs, you can propagate the block descriptions into specific XML tags in the generated code. The IDEs use the tags to create a readable description of the function blocks in the IDE.

- For Rockwell Automation RSLogix 5000 AOI/routine target IDEs, the coder propagates block descriptions from the model into the L5X AdditionalHelpText XML tag. The IDE can then import the tag as part of AOI and routine definition in the generated code.

- For CODESYS 3.5 IDE, the coder propagates block descriptions from the model into the documentation XML tag. When you import the generated code into the CODESYS 3.5 IDE, the IDE parses the content of this tag and provides readable descriptions of the function blocks in your code.

To propagate block descriptions to comments:

- **1** Enter a description for the block.

- a Right-click the block for which you want to write a description and select **Properties**.

- **b** On the **General** tab, enter a block description.

- 2 Before code generation, specify that block descriptions must propagate to code comments.

- a Right-click the subsystem for which you are generating code and select **PLC Code** > **Options**.

- **b** Select the option Include block description on page 13-16.

Your block description appears as comments in the generated code.

## Files Generated by Simulink PLC Coder

The Simulink PLC Coder software generates Structured Text code and stores it according to the target IDE platform. These platform-specific paths are default locations for the generated code. To customize generated file names, see "Specify Custom Names for Generated Files" on page 1-13.

| Platform                                                 | Generated Files                                                                                                                                                                                                                                                                   |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CODESYS 2.3                                              | <pre>current_folder\plcsrc\model_name.exp — Structured Text file for importing to the target IDE.</pre>                                                                                                                                                                           |  |

| CODESYS 3.5                                              | <pre>current_folder\plcsrc\model_name.xml — Structured Text file for importing to the target IDE.</pre>                                                                                                                                                                           |  |

| B&R Automation<br>Studio <sup>®</sup> IDE                | The following files in <i>current_folder</i> \plcsrc\model_name — Files for importing to t target IDE:                                                                                                                                                                            |  |

|                                                          | • Package.pkg — (If test bench is generated) Top-level package file for function blocks library and test bench main program in XML format.                                                                                                                                        |  |

|                                                          | In the main folder (if test bench is generated):                                                                                                                                                                                                                                  |  |

|                                                          | • IEC.prg — Test bench main program definition file in XML format.                                                                                                                                                                                                                |  |

|                                                          | • mainInit.st — Text file. Test bench init program file in Structured Text.                                                                                                                                                                                                       |  |

|                                                          | • mainCyclic.st — Text file. Test bench cyclic program file in Structured Text.                                                                                                                                                                                                   |  |

|                                                          | • mainExit.st — Text file. Test bench exit program file in Structured Text.                                                                                                                                                                                                       |  |

|                                                          | • main.typ — Text file. Main program type definitions file in Structured Text.                                                                                                                                                                                                    |  |

|                                                          | • main.var — Text file. Main program variable definitions file in Structured Text.                                                                                                                                                                                                |  |

| Beckhoff <sup>®</sup><br>TwinCAT <sup>®</sup> 2.11       | <pre>current_folder\plcsrc\model_name.exp — Structured Text file for importing to the target IDE.</pre>                                                                                                                                                                           |  |

| Beckhoff<br>TwinCAT 3                                    | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file for importing to the target IDE.                                                                                                                                                                              |  |

| KW-Software<br>MULTIPROG® 5.0                            | <pre>current_folder\plcsrc\model_name.xml — Structured Text file, in XML format, for<br/>importing to the target IDE.</pre>                                                                                                                                                       |  |

| Phoenix Contact <sup>®</sup><br>PC WORX <sup>™</sup> 6.0 | <pre>current_folder\plcsrc\model_name.xml — Structured Text file, in XML format, for<br/>importing to the target IDE.</pre>                                                                                                                                                       |  |

| Rockwell<br>Automation<br>Studio 5000 IDE:<br>AOI        | <pre>current_folder\plcsrc\model_name.L5X — (If test bench is generated) Structured<br/>Text file for importing to the target IDE using Add-On Instruction (AOI) constructs. This file<br/>is in XML format and contains the generated Structured Text code for your model.</pre> |  |

| Platform                                                   | Generated Files                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Rockwell<br>Automation<br>Studio 5000 IDE:                 | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated) Structured<br>Text file for importing to the target IDE using routine constructs. This file is in XML format<br>and contains the generated Structured Text code for your model.                                       |  |

| Routine                                                    | In <i>current_folder</i> \plcsrc\model_name (if test bench is not generated), the following files are generated:                                                                                                                                                                                  |  |

|                                                            | • <i>subsystem_block_name</i> .L5X — Structured Text file in XML format. Contains program tag and UDT type definitions and the routine code for the top-level subsystem block.                                                                                                                    |  |

|                                                            | • <i>routine_name</i> .L5X — Structured Text files in XML format. Contains routine code for other subsystem blocks.                                                                                                                                                                               |  |

| Rockwell<br>Automation<br>RSLogix 5000<br>IDE: AOI         | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated) Structured<br>Text file for importing to the target IDE using Add-On Instruction (AOI) constructs. This file<br>is in XML format and contains the generated Structured Text code for your model.                      |  |

| Rockwell<br>Automation<br>RSLogix 5000<br>IDE: Routine     | <i>current_folder</i> \plcsrc\model_name.L5X — (If test bench is generated) Structured<br>Text file for importing to the target IDE using routine constructs. This file is in XML format<br>and contains the generated Structured Text code for your model.                                       |  |

|                                                            | In <i>current_folder</i> \plcsrc\model_name (if test bench is not generated), the following files are generated:                                                                                                                                                                                  |  |

|                                                            | • <i>subsystem_block_name</i> .L5X — Structured Text file in XML format. Contains program tag and UDT type definitions and the routine code for the top-level subsystem block.                                                                                                                    |  |

|                                                            | • <i>routine_name</i> .L5X — Structured Text files in XML format. Contains routine code for other subsystem blocks.                                                                                                                                                                               |  |

| Siemens<br>SIMATIC <sup>®</sup> STEP <sup>®</sup><br>7 IDE | <pre>current_folder\plcsrc\model_name\model_name.scl — Structured Text file for<br/>importing to the target IDE.</pre>                                                                                                                                                                            |  |

|                                                            | <pre>current_folder\plcsrc\model_name\model_name.asc — (If test bench is generated) Text file. Structured Text file and symbol table for generated test bench code.</pre>                                                                                                                         |  |

| Siemens TIA<br>Portal IDE                                  | <pre>current_folder\plcsrc\model_name\model_name.scl — Structured Text file for<br/>importing to the target IDE.</pre>                                                                                                                                                                            |  |

| Generic                                                    | <i>current_folder</i> \plcsrc\model_name.st — Pure Structured Text file. If your target IDE is not available for the Simulink PLC Coder product, consider generating and importing a generic Structured Text file.                                                                                |  |

| PLCopen XML                                                | <i>current_folder</i> \plcsrc\model_name.xml — Structured Text file formatted using the PLCopen XML standard. If your target IDE is not available for the Simulink PLC Coder product, but uses a format like this standard, consider generating and importing a PLCopen XML Structured Text file. |  |

| Bosch Rexroth<br>IndraWorks                                | <pre>current_folder\plcsrc\model_name.xml — Structured Text file for importing to the target IDE.</pre>                                                                                                                                                                                           |  |

| OMRON Sysmac<br>Studio                                     | <pre>current_folder\plcsrc\model_name.xml — Structured Text file for importing to the target IDE.</pre>                                                                                                                                                                                           |  |

#### **Specify Custom Names for Generated Files**

The Simulink PLC Coder software generates Structured Text code and stores it according to the target IDE platform. These platform-specific paths are default locations for the generated code. For more information, see "Files Generated by Simulink PLC Coder" on page 1-11.

To specify a different name for the generated files, set the **Function name options** parameter in the Subsystem block:

- 1 Right-click the Subsystem block for which you want to generate code and select Subsystem Parameters.

- 2 In the Main tab, select the Treat as atomic unit check box.

- **3** Click the **Code Generation** tab.

- 4 From the **Function Packaging** parameter list, select **Reusable Function**.

These options enable the Function name options and File name options parameters.

**5** Select the option that you want to use for generating the file name.

| Function name options | Generated File Name                                                                                                                                    |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto                  | Default. Uses the model name, as listed in<br>"Prepare Model for Structured Text<br>Generation" on page 1-3, for example,<br>plcdemo_simple_subsystem. |

| Use subsystem name    | Uses the subsystem name, for example,<br>SimpleSubsystem.                                                                                              |

| User specified        | Uses the custom name that you specify in the <b>Function name</b> parameter, for example, SimpleSubsystem.                                             |

## Import Structured Text Code Automatically

#### In this section...

"PLC IDEs for Importing Code Automatically" on page 1-14

"Generate and Automatically Import Structured Text Code" on page 1-14

"Troubleshoot Automatic Import Issues" on page 1-14

#### PLC IDEs for Importing Code Automatically

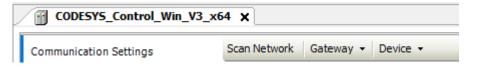

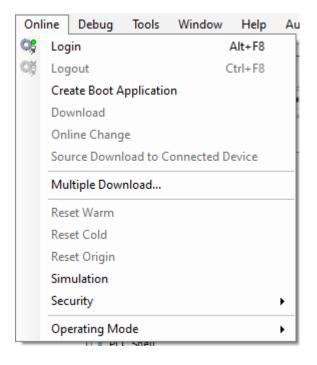

You can generate and automatically import structured text code to the CODESYS Version 2.3 target PLC IDE.

#### Generate and Automatically Import Structured Text Code

You can generate and automatically import structured text code. Before you start:

- In the target IDE, save your current project.

- Close open projects.

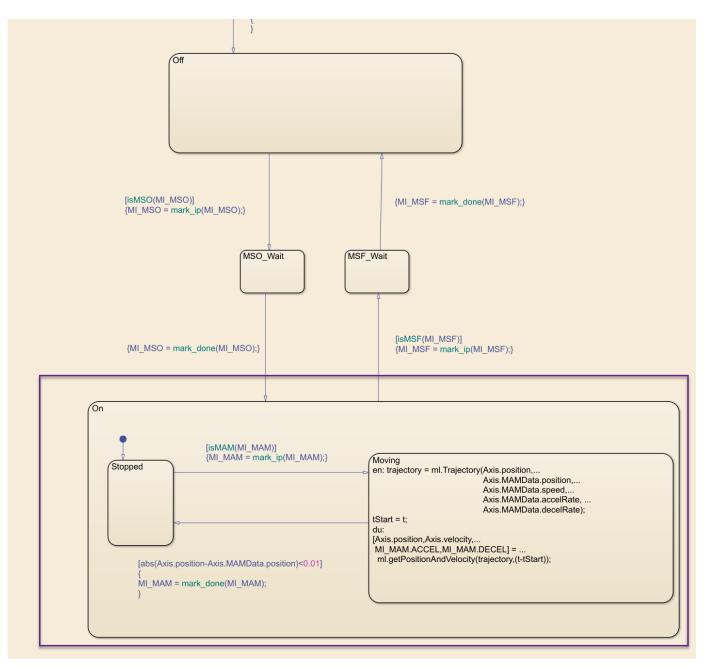

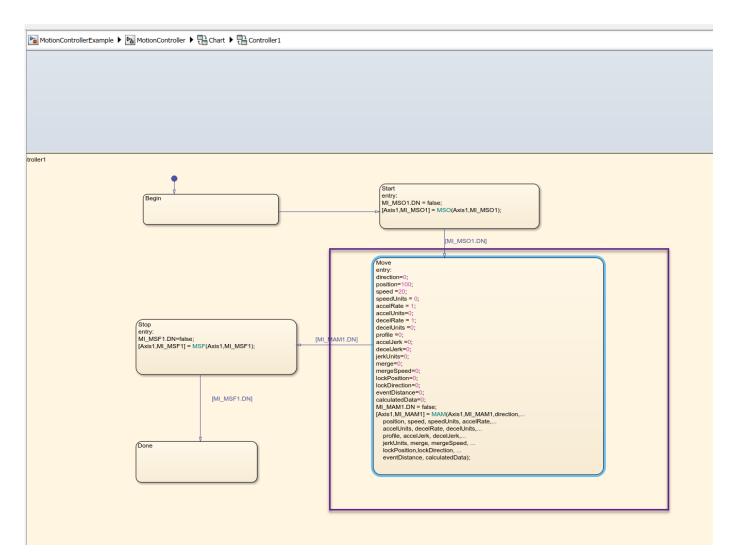

- Close the target IDE and target IDE-related windows.